- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366692 > CAT24FC64GLETE13 64K-Bit I2C Serial CMOS EEPROM PDF資料下載

參數(shù)資料

| 型號: | CAT24FC64GLETE13 |

| 元件分類: | EEPROM |

| 英文描述: | 64K-Bit I2C Serial CMOS EEPROM |

| 中文描述: | 64K的位I2C串行CMOS EEPROM的 |

| 文件頁數(shù): | 7/10頁 |

| 文件大?。?/td> | 635K |

| 代理商: | CAT24FC64GLETE13 |

DsconinuedPat

CAT24FC64

7

Doc No. 1046, Rev. K

2005 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

READ OPERATIONS

The READ operation for the CAT24FC64 is initiated in

the same manner as the write operation with one

exception, that R/

W

bit is set to one. Three different

READ operations are possible: Immediate/Current

Address READ, Selective/Random READ and

Sequential READ.

The CAT24FC64

’

s address counter contains the address

of the last byte accessed, incremented by one. In other

words, if the last READ or WRITE access was to address

N, the READ immediately following would access data

from address N+1. If N=E (where E=8,191), then the

counter will

‘

wrap around

’

to address 0 and continue to

clock out data. After the CAT24FC64 receives its slave

address information (with the R/

W

bit set to one), it

issues an acknowledge, then transmits the 8 bit byte

requested. The master device does not send an

acknowledge, but will generate a STOP condition.

Selective/Random Read

Selective/Random READ operations allow the Master

device to select at random any memory location for a

READ operation. The Master device first performs a

‘

dummy

’

write operation by sending the START condition,

slave address and byte addresses of the location it

wishes to read. After CAT24FC64 acknowledges, the

Master device sends the START condition and the slave

address again, this time with the R/

W

bit set to one. The

CAT24FC64 then responds with its acknowledge and

sends the 8-bit byte requested. The master device does

not send an acknowledge but will generate a STOP

condition.

The Sequential READ operation can be initiated by

either the Immediate Address READ or Selective READ

operations. After the CAT24FC64 sends the initial 8-bit

byte requested, the Master will respond with an

acknowledge which tells the device it requires more

data. The CAT24FC64 will continue to output an 8-bit

byte for each acknowledge sent by the Master. The

operation will terminate when the Master fails to respond

with an acknowledge, thus sending the STOP condition.

The data being transmitted from CAT24FC64 is outputted

sequentially with data from address N followed by data

from address N+1. The READ operation address counter

increments all of the CAT24FC64 address bits so that

the entire memory array can be read during one operation.

If more than E (where E=8,191) bytes are read out, the

counter will

‘

wrap around

’

and continue to clock out data

bytes.

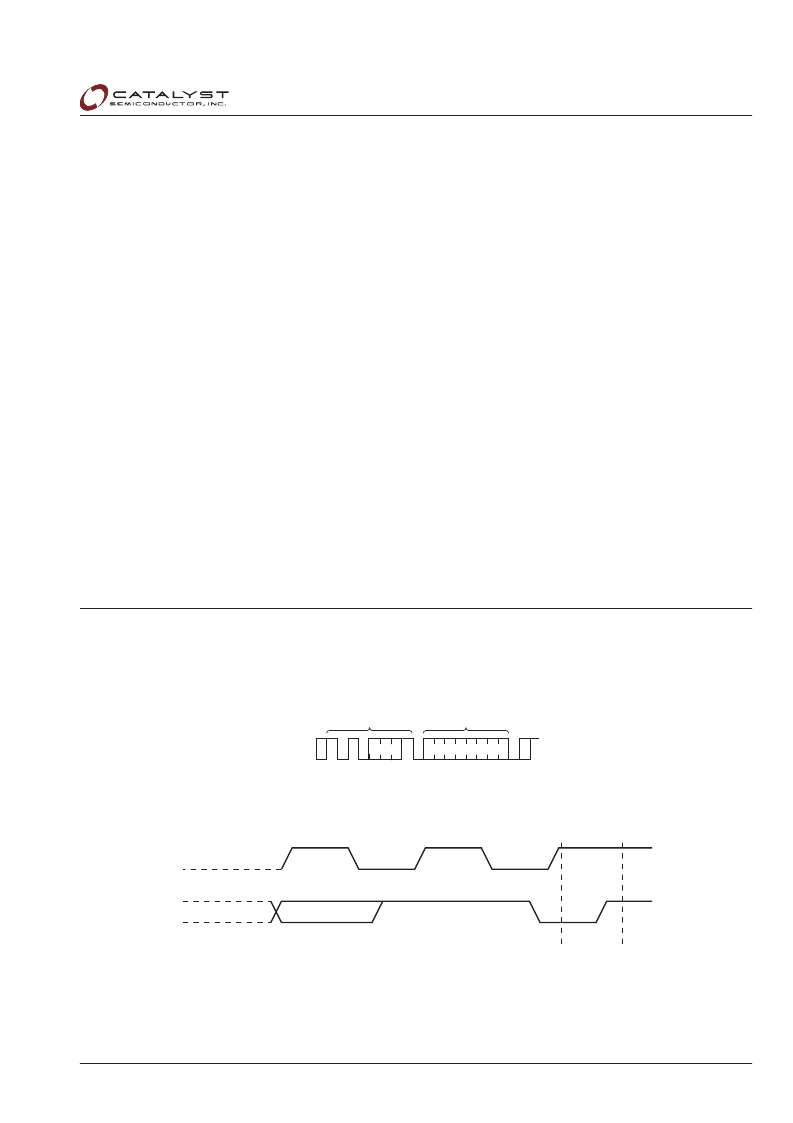

Figure 8. Immediate Address Read Timing

SCL

SDA

8TH BIT

STOP

NO ACK

DATA OUT

8

9

SLAVE

ADDRESS

S

A

C

K

BUS ACTIVITY:

MASTER

SDA LINE

S

T

A

R

T

N

O

A

C

K

DATA

S

T

O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT24FC64GLITE13 | 64K-Bit I2C Serial CMOS EEPROM |

| CAT24FC64GWETE13 | 64K-Bit I2C Serial CMOS EEPROM |

| CAT24FC64GWITE13 | 64K-Bit I2C Serial CMOS EEPROM |

| CAT24WC02 | 2K-Bit IIC Serial CMOS EEPROM(2K位(256字x8位)IIC串行CMOS EEPROM) |

| CAT24WC04 | 4K-Bit IIC Serial CMOS EEPROM(4K位(512字x8位)IIC串行CMOS EEPROM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT24FC64LI | 制造商:Rochester Electronics LLC 功能描述: 制造商:Catalyst Semiconductor 功能描述: |

| CAT24FC64WI-TE13 | 制造商:Catalyst Semiconductor 功能描述: |

| CAT24FC64YI | 制造商:Rochester Electronics LLC 功能描述: 制造商:Catalyst Semiconductor 功能描述: |

| CAT24FC64YI-TE13 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Catalyst Semiconductor 功能描述: |

| CAT24G | 制造商:Semiconductors 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。