- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369653 > CAT22C10W-20-TE13 256-Bit Nonvolatile CMOS Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | CAT22C10W-20-TE13 |

| 英文描述: | 256-Bit Nonvolatile CMOS Static RAM |

| 中文描述: | 256位非易失性的CMOS靜態(tài)RAM |

| 文件頁(yè)數(shù): | 8/10頁(yè) |

| 文件大小: | 514K |

| 代理商: | CAT22C10W-20-TE13 |

CAT22C10

8

Doc. No. 1082, Rev. O

Recall

At anytime, except during a store operation, taking the

RECALL

pin low will initiate a recall operation. This is

independent of the state of

CS

,

WE

, or A

0

–A

5

. After the

RECALL

pin has been held low for the duration of the

Recall Pulse Width (t

RCP

), the recall will continue inde-

pendent of any other inputs. During the recall, the entire

contents of the EEPROM array is transferred to the

Static RAM array. The first byte of data may be externally

accessed after the recalled data access time from end of

recall (t

ARC

) is met. After this, any other byte may be

accessed by using the normal read mode.

If the

RECALL

pin is held low for the entire Recall Cycle

time (t

RCC

), the contents of the Static RAM may be

immediately accessed by using the normal read mode.

A recall operation can be performed an unlimited num-

ber of times without affecting the integrity of the data.

The outputs I/O

0

–I/O

3

will go into the high impedance

state as long as the

RECALL

signal is held low.

Store

At any time, except during a recall operation, taking the

STORE

pin low will initiate a store operation. This takes

place independent of the state of

CS

,

WE

or A

0

–A

5

. The

STORE

pin must be held low for the duration of the Store

Pulse Width (t

STP

) to ensure that a store operation is

initiated. Once initiated, the

STORE

pin becomes a

“Don’t Care”, and the store operation will complete its

transfer of the entire contents of the Static RAM array

into the EEPROM array within the Store Cycle time

(t

STC

). If a store operation is initiated during a write cycle,

the contents of the addressed Static RAM byte and its

corresponding byte in the EEPROM array will be un-

known.

During the store operation, the outputs are in a high

impedance state. A minimum of 100,000 store opera-

tions can be performed reliably and the data written into

the EEPROM array has a minimum data retention time

of 10 years.

DATA PROTECTION DURING POWER-UP AND

POWER-DOWN

The CAT22C10 has on-chip circuitry which will prevent

a store operation from occurring when V

CC

falls below

3.0V typ. This function eliminates the potential hazard of

spurious signals initiating a store operation when the

system power is below 3.0V typ.

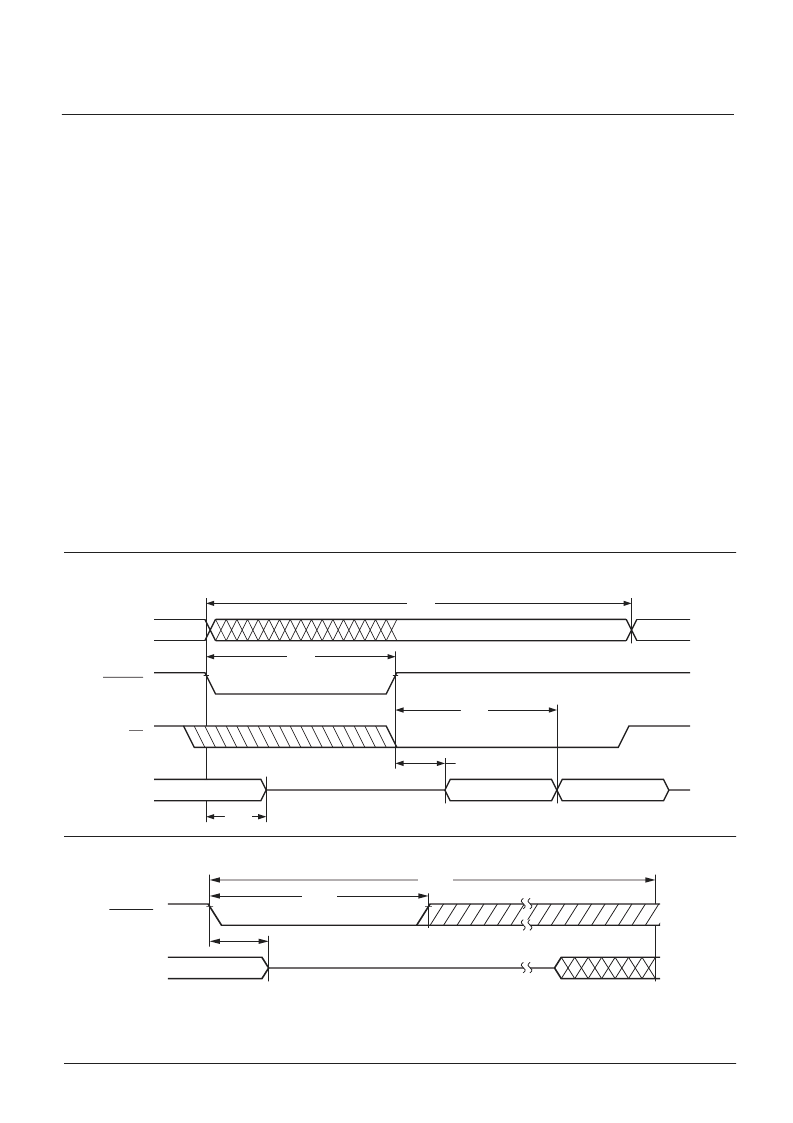

Figure 4. Recall Cycle Timing

Figure 5. Store Cycle Timing

CS

DATA I/O

RECALL

ADDRESS

DATA UNDEFINED

DATA VALID

HIGH-Z

tRCZ

tORC

tARC

tRCP

tRCC

STORE

DATA I/O

tSTZ

HIGH-Z

tSTP

tSTC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT22C10W-30-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WA-20-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WA-30-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WI-20-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WI-30-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT22C10W-30 | 制造商:ON Semiconductor 功能描述:256-BIT N V CMOS STATIC RAM - Rail/Tube |

| CAT22C10W-30TE13 | 制造商:ON Semiconductor 功能描述:256-BIT N V CMOS STATIC RAM - Tape and Reel |

| CAT22C10W-30-TE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WA-20-TE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WA-30-TE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:256-Bit Nonvolatile CMOS Static RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。