- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369516 > BT458LPJ110 Video DAC with Color Palette (RAMDAC) PDF資料下載

參數(shù)資料

| 型號(hào): | BT458LPJ110 |

| 英文描述: | Video DAC with Color Palette (RAMDAC) |

| 中文描述: | 視頻DAC的調(diào)色板(的RAMDAC) |

| 文件頁(yè)數(shù): | 23/60頁(yè) |

| 文件大?。?/td> | 647K |

| 代理商: | BT458LPJ110 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

Bt457/Bt458

2.0 Registers

125 MHz/135 MHz/165 MHz Monolithic CMOS 256 Color Palette RAMDAC

2.5 Bt457 Control/Test Register

L45801 Rev. N

Conexant

2-5

2.5 Bt457 Control/Test Register

The control/test register provides diagnostic capability by enabling the MPU to

read the D/A converter inputs. It can be written to or read by the MPU at any time

and is not initialized. For proper operation, it must be initialized by the user after

power-up. When writing to the register, the upper four bits (D[7:4]) are ignored.

The contents of the test register are defined as follows:

To use the control/test register, the MPU writes to it, specifying the low or

high nibble of color information. When the MPU reads the register, the four bits

of color information from the DAC inputs are contained in the upper four bits,

and the lower four bits contain whatever was previously written to the register.

Either the CLOCK must be slowed down to the MPU cycle time, or the same

pixel and overlay data must be presented to the device during the entire MPU read

cycle.

The red, green, and blue enable bits specify the mode in which color data is

written to and read from, the Bt457. If all three enable bits are logical 0s, each

write cycle to the color palette RAM or overlay registers loads 8 bits of color data.

During each read cycle of the color palette RAM or overlay registers, 8 bits of

color data are output onto the data bus. If a 24-bit data bus is available, three

Bt457s can be accessed simultaneously.

If any of the red, green, or blue enable bits is a logical 1, the Bt457 assumes

the MPU is reading and writing color information using red-green-blue cycles,

such as are used in the Bt458. Setting the appropriate enable bit configures the

Bt457 to output or input color data only for the color read/write cycle

corresponding to the enabled color. Thus, if the green enable bit is a logical 1, and

a red-green-blue write cycle occurred, the Bt457 would input data only during the

green write cycle. If a red-green-blue read cycle occurred, the Bt457 would output

data only during the green read cycle. CE* must be a logical 0 during each of the

red-green-blue cycles. Only one of the enable bits must be a logical 1. This mode

of operation is useful when only an 8-bit data bus is available and the software

drivers are written for RGB operation.

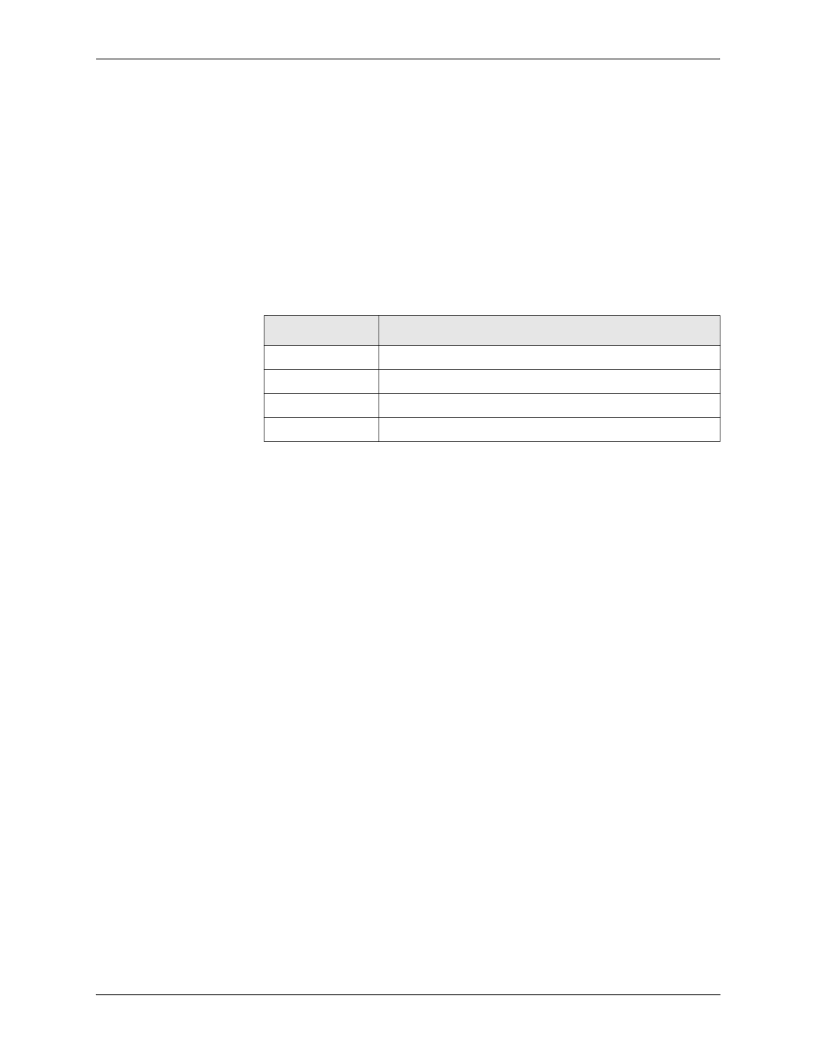

Table 2-3. Bt457 Control Test Register

D[7:4]

Color Information

D[3]

Low (Logical 1) or High (Logical 0) Nibble

D[2]

Blue Channel Enable

D[1]

Green Channel Enable

D[0]

Red Channel Enable

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BT458LPJ125 | Video DAC with Color Palette (RAMDAC) |

| BT458LPJ135 | Video DAC with Color Palette (RAMDAC) |

| BT458LPJ165 | Video DAC with Color Palette (RAMDAC) |

| BT458LPJ80 | Video DAC with Color Palette (RAMDAC) |

| BT457KG125 | Video DAC with Color Palette (RAMDAC) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BT458LPJ125 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Video DAC with Color Palette (RAMDAC) |

| BT458LPJ135 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Video DAC with Color Palette (RAMDAC) |

| BT458LPJ165 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Video DAC with Color Palette (RAMDAC) |

| BT458LPJ80 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Video DAC with Color Palette (RAMDAC) |

| BT471KPJ35-695 | 制造商:BT 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。