- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369396 > B9948CA TWELVE DISTRIBUTED-OUTPUT CLOCK DRIVER|TQFP|32PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | B9948CA |

| 英文描述: | TWELVE DISTRIBUTED-OUTPUT CLOCK DRIVER|TQFP|32PIN|PLASTIC |

| 中文描述: | 第十二章分布式輸出時鐘驅(qū)動器| TQFP封裝| 32腳|塑料 |

| 文件頁數(shù): | 3/6頁 |

| 文件大小: | 60K |

| 代理商: | B9948CA |

B9948

Document #: 38-07079 Rev. *B

Page 3 of 6

Maximum Ratings

Maximum Input Voltage Relative to V

SS

:............ V

SS

–

0.3V

Maximum Input Voltage Relative to V

DD

:.............V

DD

+ 0.3V

Storage Temperature: .................................-65

°

C to + 150

°

C

Operating Temperature:.................................-40

°

C to +85

°

C

Maximum ESD Protection.............................................. 2 KV

Maximum Power Supply: ................................................5.5V

Maximum Input Current:

..................................................±

20 mA

This device contains circuitry to protect the inputs against

damage due to high static voltages or electric field; however,

precautions should be taken to avoid application of any volt-

age higher than the maximum rated voltages to this circuit. For

proper operation, V

in

and V

out

should be constrained to the

range:

V

SS

< (V

in

or V

out

) < V

DD

Unused inputs must always be tied to an appropriate logic volt-

age level (either V

SS

or V

DD

).

Notes:

2.

3.

Inputs have pull-up resistors that effect input current, PECL_CLK# has a pull-down resistor.

The V

is the difference from the most positive side of the differential input signal. Normal operation is obtained when the

“

High

”

input is within the V

CMR

range and the input lies within the V

specification.

Driving series or parallel terminated 50

(or 50

to V

DD

/2) transmission lines.

4.

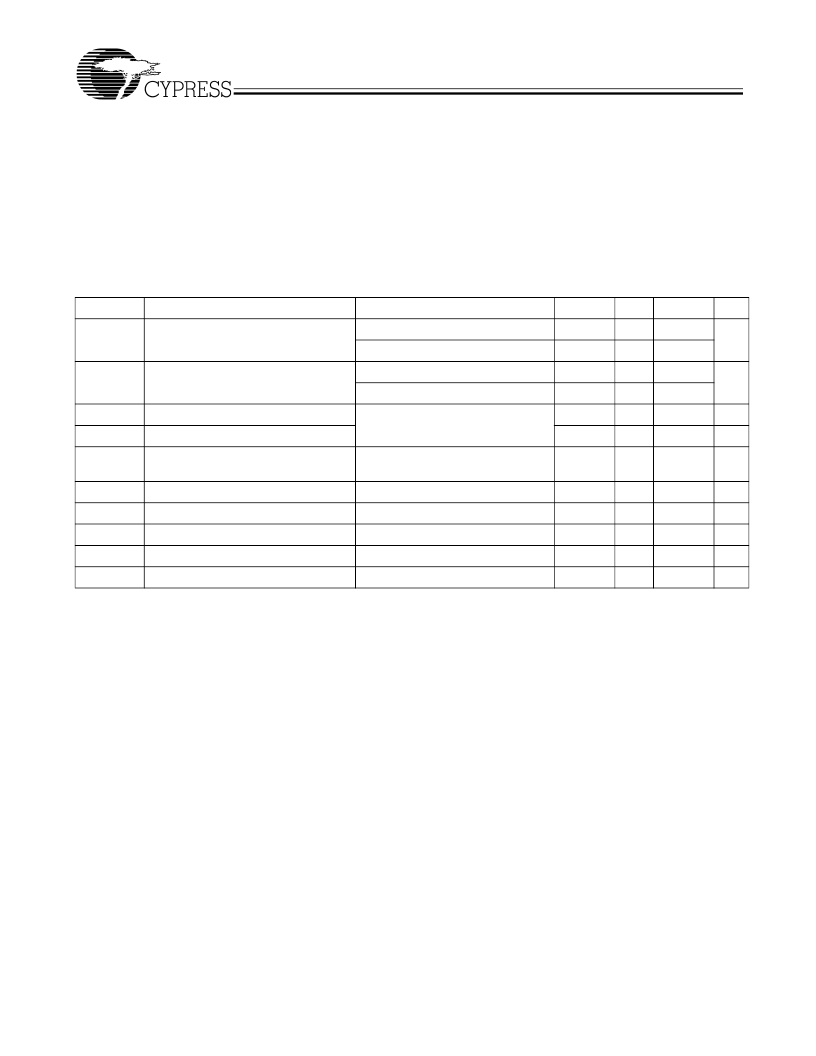

DC Parameters:

V

DDC

= 3.3V ±10%, V

DD

= 3.3V ±10%, T

A

=

–

40

°

C to +85

°

C

Parameter

Description

Conditions

Min.

Typ.

Max.

Unit

V

IL

Input Low Voltage

PECL_CLK, Single Ended

1.49

1.825

V

All other inputs

V

SS

2.135

0.8

V

IH

Input High Voltage

PECL_CLK, Single Ended

2.42

V

All other inputs

2.0

V

DD

–

100

I

IL

I

IH

V

PP

Input Low Current (@V

IL

= V

SS

)

Input High Current (@V

IL

=V

DD

)

Peak-to-Peak Input Voltage

PECL_CLK

Note 2

μA

100

μA

Note 3

300

1000

mV

V

CMR

V

OL

V

OH

I

DD

C

in

Common Mode Range PECL_CLK

V

DD

–

2.0

V

DD

–

0.6

0.4

V

Output Low Voltage

I

OL

= 20 mA, Note 4

I

OH

=

–

20 mA, V

DDC

= 3.3V, Note 4

All V

DDC

and V

DD

V

Output High Voltage

2.5

V

Quiescent Supply Current

1

2

mA

Input Capacitance

4

pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| B9948 | 3.3V, 160-MHz, 1:12 Clock Distribution Buffer |

| B9APCB | SOCKET VALVE PCB 9 PIN |

| BA00 | |

| BA05 | |

| BA06 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| B9948L | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:2.5V/3.3V, 160-MHz, 1:12 Clock Distribution Buffer |

| B9948LAA | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:2.5V/3.3V, 160-MHz, 1:12 Clock Distribution Buffer |

| B9949 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V 160-MHz 1:15 Clock Distribution Buffer |

| B9949CA | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V 160-MHz 1:15 Clock Distribution Buffer |

| B9951 | 制造商:Thomas & Betts 功能描述:KINDORF B |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。