- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19626 > ATF2500C-20JI (Atmel)IC CPLD EE 20NS 44PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | ATF2500C-20JI |

| 廠商: | Atmel |

| 文件頁數(shù): | 20/24頁 |

| 文件大小: | 0K |

| 描述: | IC CPLD EE 20NS 44PLCC |

| 標(biāo)準(zhǔn)包裝: | 27 |

| 系列: | ATF2500C(L) |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時(shí)間 tpd(1): | 20.0ns |

| 電壓電源 - 內(nèi)部: | 4.5 V ~ 5.5 V |

| 宏單元數(shù): | 24 |

| 輸入/輸出數(shù): | 24 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 44-PLCC |

| 包裝: | 管件 |

5

0777K–PLD–1/24/08

ATF2500C

5.

Preload and Observability of Registered Outputs

The ATF2500Cs registers are provided with circuitry to allow loading of each register asynchro-

nously with either a high or a low. This feature will simplify testing since any state can be forced

into the registers to control test sequencing. A V

IH level on the odd I/O pins will force the appro-

priate register high; a V

IL will force it low, independent of the polarity or other configuration bit

settings.

The PRELOAD state is entered by placing an 10.25V to 10.75V signal on SMP lead 42. When

the preload clock SMP lead 23 is pulsed high, the data on the I/O pins is placed into the 12 reg-

isters chosen by the Q select and even/odd select pins.

Register 2 observability mode is entered by placing an 10.25V to 10.75V signal on pin/lead 2. In

this mode, the contents of the buried register bank will appear on the associated outputs when

the OE control signals are active.

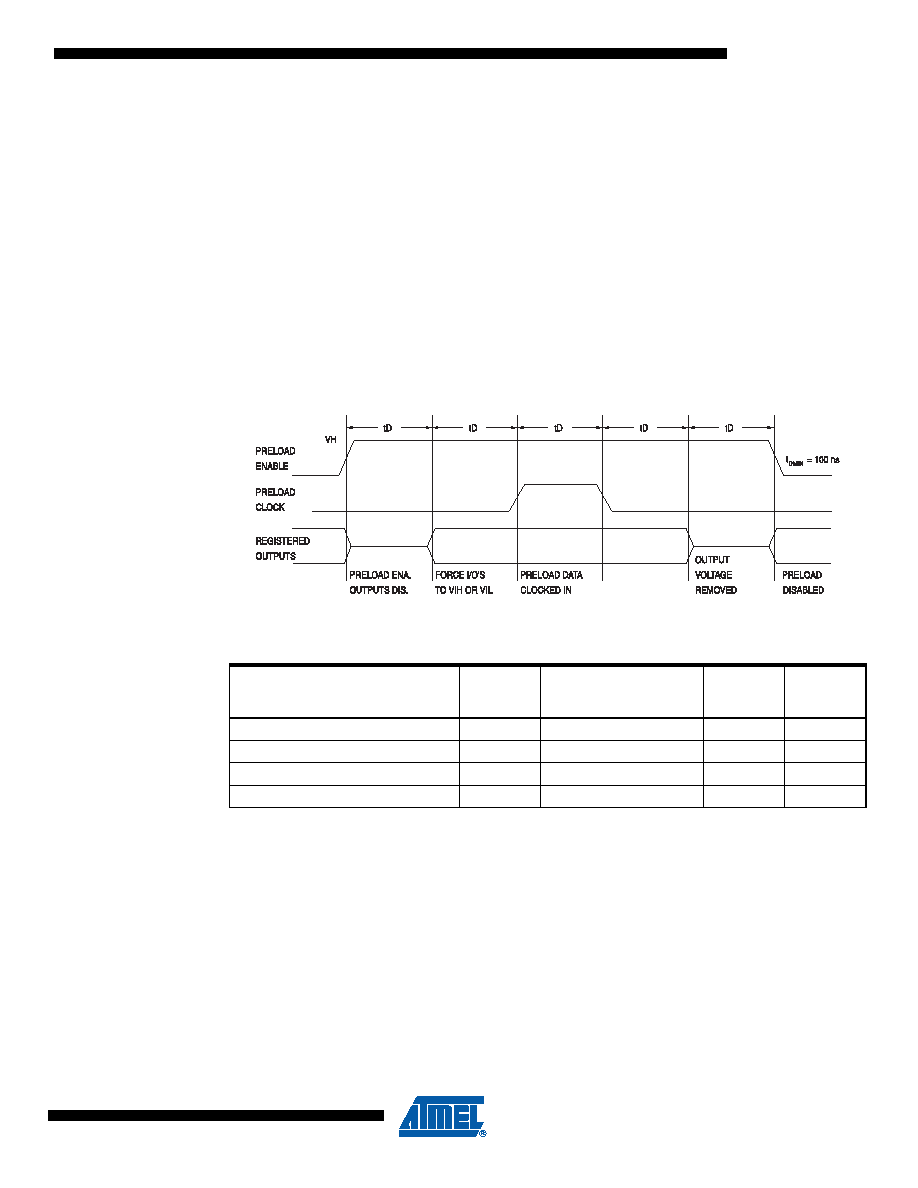

Figure 5-1.

Preload Waveforms

Table 5-1.

Preload Levels

Level Forced on Odd

I/O Pin during

PRELOAD Cycle

Q Select

Pin State

Even/Odd

Select

Even Q1

State after

Cycle

Even Q2

State after

Cycle

Odd Q1

State after

Cycle

Odd Q2

State after

Cycle

V

IH/VIL

Low

High/Low

X

V

IH/VIL

High

Low

X

High/Low

X

V

IH/VIL

Low

High

X

High/Low

X

V

IH/VIL

High

X

High/Low

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5LV-256/120-10YI | IC CPLD 256MC 120I/O 160PQFP |

| NTA1205MC | CONV DC/DC SM 1W 12VIN 5V DL 1KV |

| SA56004BDP,118 | IC TEMP SENSOR 8-TSSOP |

| V300A2E160BF | CONVERTER MOD DC/DC 2V 160W |

| MIC5239-5.0BM | IC REG LDO 5V .5A 8-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATF2500C-20KM | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 STD PWR 2500 GATE 24 MACROCELL 5V RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF2500C-20LM | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 ASICS RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF2500C-20PC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 2500 GATE 24 MACRO STD PWR 5V-20NS RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF2500C-20PI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 2500 GATE 24 MACRO STD PWR 5V-20NS RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF2500C-20PU | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 20 ns 24 I/O Pins 24 macorcells 48 reg RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。