- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C90JCTR (ADVANCED MICRO DEVICES INC) KPTC6CG10-6P PDF資料下載

參數(shù)資料

| 型號: | AM79C90JCTR |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | KPTC6CG10-6P |

| 中文描述: | 1 CHANNEL(S), LOCAL AREA NETWORK CONTROLLER, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 22/62頁 |

| 文件大小: | 437K |

| 代理商: | AM79C90JCTR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

AMD

P R E L I M I N A R Y

22

Am79C90

Bit

Name

Description

03

TDMD

TRANSMIT DEMAND, when set,

causes the C-LANCE to access the

Transmit Descriptor Ring without

waiting for the polltime interval to

elapse. TDMD need not be set to

transmit a packet; it merely hastens

the C-LANCE’s response to a Trans-

mit Descriptor Ring entry insertion by

the host.

TDMD is WRITE WITH ONE ONLY

and is cleared by the microcode after

it is used. It may read as a “1” for a

short time after it is written because

the microcode may have been busy

when TDMD was set. It is also

cleared by

RESET

or by setting the

STOP bit. Writing a “0” in this bit has

no effect.

STOP disables the C-LANCE from

all external activity when set and

clears the internal logic. Setting

STOP is the equivalent of asserting

RESET

. The C-LANCE remains in-

active and STOP remains set until

the STRT or INIT bit is set. If STRT,

INIT and STOP are all set together,

STOP will override the other bits and

only STOP will be set.

STOP is READ/WRITE WITH ONE

ONLY and set by RESET. Writing a

“0” to this bit has no effect. STOP is

cleared by setting either INIT or

STRT. CSR

3

must be reloaded

when the STOP bit is set.

START enables the C-LANCE to

send and receive packets, perform

direct memory access, and do buffer

management. The STOP bit must be

set prior to setting the STRT bit. Set-

ting STRT clears the STOP bit.

STRT is READ/WRITE and is set

with one only. Writing a “0” into this

bit has no effect. STRT is cleared by

RESET

or by setting the STOP bit.

INITIALIZE, when set, causes the

C-LANCE to begin the initialization

procedure and access the Initializa-

tion Block. The STOP bit must be set

prior to setting the INIT bit. Setting

INIT clears the STOP bit.

INIT is READ/WRITE WITH “1”

ONLY. Writing a “0” into this bit has

no effect. INIT is cleared by

RESET

or by setting the STOP bit.

The C-LANCE latches CSR

0

during

a slave read; therefore, the CSR

0

status bits are guaranteed to be sta-

ble for the duration of the CSR

0

access.

02

STOP

01

STRT

00

INIT

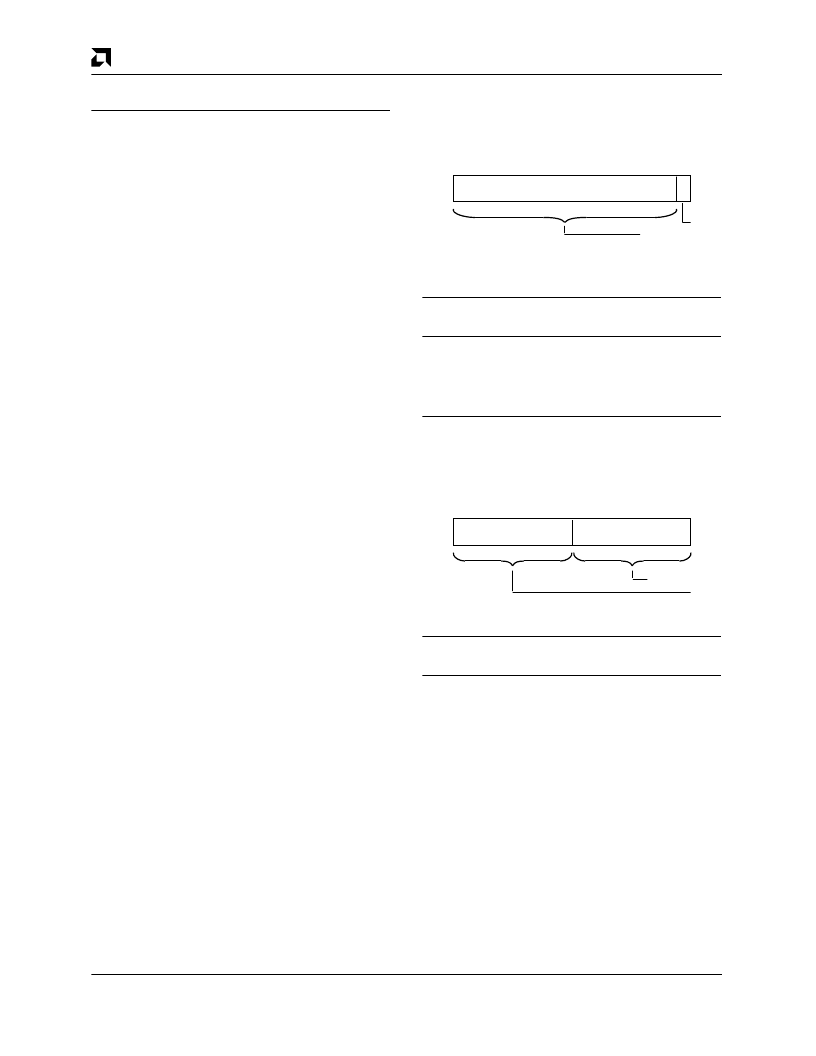

Control and Status Register 1 (CSR1)

READ/WRITE:

Accessible only when the STOP bit

of CSR

0

is a ONE and RAP = 01.

The C-LANCE preserves the con-

tents of CSR

1

after STOP.

‘0’

15

1 0

IADR

(15:01)

17881B-16

Bit

Name

Description

15:01

IADR

The low order 15 bits of the address

of the first word (lowest address) in

the Initialization Block.

Must be zero.

00

Control and Status Register 2 (CSR2)

READ/WRITE:

Accessible only when the STOP bit

of CSR

0

is a ONE and RAP = 10.

The C-LANCE preserves the con-

tents of CSR

2

after STOP.

8 7

15

0

IADR (23:16)

17881B-17

RES

Bit

Name

Description

15:08

RES

Reserved. Read as zeroes. Write as

zeroes.

The high order 8 bits of the address

of the first word (lowest address) in

the initialization Block.

07:00

IADR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C90PC | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90PCTR | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C930 | PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

| AM79C930VCW | PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

| AM79C940VCW | Media Access Controller for Ethernet (MACE) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C90PC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90PCB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C90PCTR | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90WW WAF | 制造商:Advanced Micro Devices 功能描述: |

| AM79C930 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。