- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362278 > AM486DXSQFP 70NS, PLCC, IND TEMP(EEPROM) PDF資料下載

參數(shù)資料

| 型號(hào): | AM486DXSQFP |

| 英文描述: | 70NS, PLCC, IND TEMP(EEPROM) |

| 中文描述: | Am486DX采用SQFP - Am486DX采用SQFP包溫度比較 |

| 文件頁(yè)數(shù): | 33/52頁(yè) |

| 文件大?。?/td> | 1242K |

| 代理商: | AM486DXSQFP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

Am486DE2 Microprocessor

33

A20M Pin

Systems based on the MS-DOS operating system con-

tain a feature that enables the CPU address bit A20 to

be forced to 0. This limits physical memory to a maxi-

mum of 1 Mbyte, and is provided to ensure compatibility

with those programs that relied on the physical address

wraparound functionality of the original IBM PC. The

A20M pin on Am486DE2 CPUs provides this function.

When A20M is active, all external bus cycles drive A20

Low, and all internal cache accesses are performed with

A20 Low.

The A20M pin is recognized while the CPU is in SMM.

The functionality of the A20M input must be recognized

in two instances:

1. If the SMI handler needs to access system memory

space above 1 Mbyte (for example, when saving

memory to disk for a zero-volt suspend), the A20M

pin must be deasserted before the memory above 1

Mbyte is addressed.

2. If SMRAM has been relocated to address space

above 1 Mbyte and A20M is active upon entering

SMM, the CPU attempts to access SMRAM at the

relocated address, but with A20 Low. This could

cause the system to crash, because there would be

no valid SMM interrupt handler at the accessed

location.

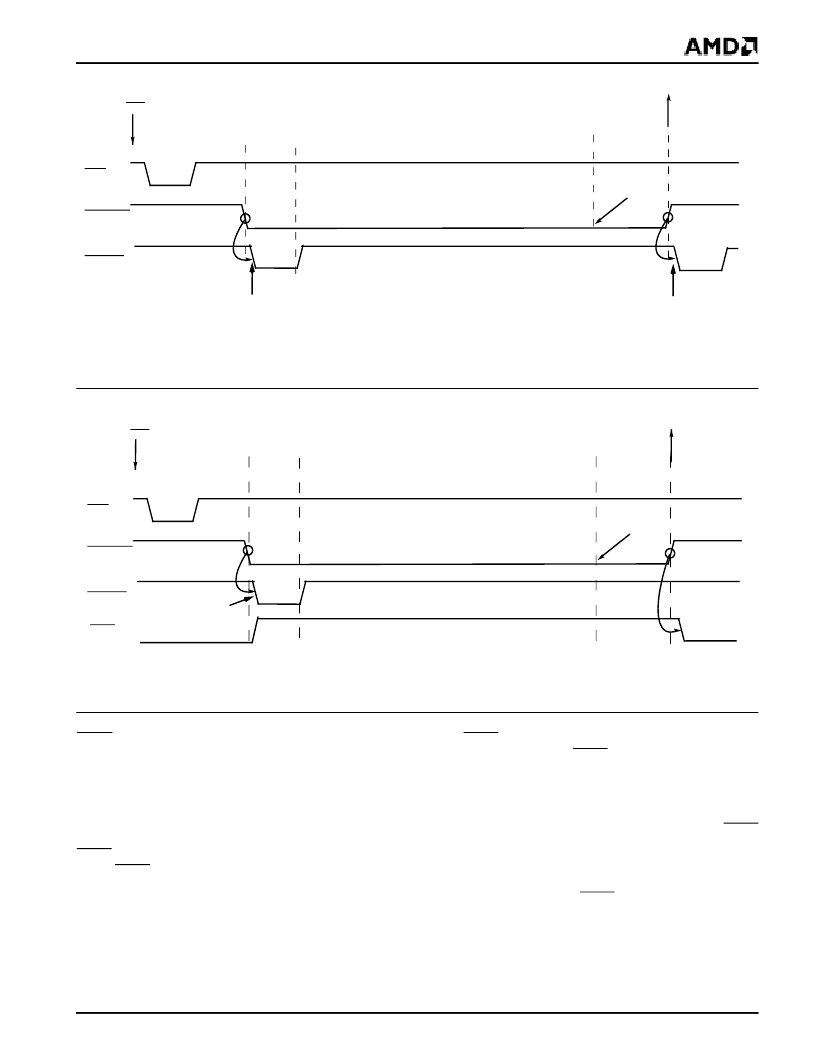

Figure 16. SMM Timing in Systems Using Overlaid Memory Space and Write-Through Mode with Caching

EnabledDuring SMM

Figure 17. SMM Timing in Systems Using Overlaid Memory Space and Write-Through Mode with Caching

DisabledDuring SMM

State

Save

SMI Handler

State

Resume

Normal

Cycle

RSM

SMI

SMIACT

FLUSH

SMI

Instruction x

Instruction x+1

Cache contents

invalidated

Cache contents

invalidated

State

Save

SMI Handler

State

Resume

Normal

Cycle

RSM

SMI

SMIACT

FLUSH

SMI

Instruction x

Instruction x+1

Cache contents

invalidated

KEN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM486 | Am486 Microprocessor Software User's Manual? 4.40MB (PDF) |

| AM49DL3208G | Am49DL3208G - Stacked Multi-Chip Package (MCP) Flash Memory and pSRAM |

| AM49DL320BG | Am49DL320BG - Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL32XBG | Am49DL32xBG - Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640BH | Am49DL640BH - Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM486-EVAL-KIT | 制造商:Advanced Micro Devices 功能描述:AM486CDP EVAL KIT |

| AM4874N | 制造商:ANALOGPOWER 制造商全稱:ANALOGPOWER 功能描述:N-Channel 30-V (D-S) MOSFET |

| AM4890N | 制造商:ANALOGPOWER 制造商全稱:ANALOGPOWER 功能描述:Dual N-Channel 150-V (D-S) MOSFET |

| AM4892N | 制造商:ANALOGPOWER 制造商全稱:ANALOGPOWER 功能描述:Dual N-Channel 150-V (D-S) MOSFET |

| AM48S-12-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。