- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376486 > AM42DL6404G85IT (SPANSION LLC) Stacked Multi-Chip Package (MCP) Flash Memory and SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | AM42DL6404G85IT |

| 廠商: | SPANSION LLC |

| 元件分類: | 存儲(chǔ)器 |

| 英文描述: | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| 中文描述: | SPECIALTY MEMORY CIRCUIT, PBGA73 |

| 封裝: | 8 X 11.60 MM, FBGA-73 |

| 文件頁數(shù): | 55/61頁 |

| 文件大小: | 567K |

| 代理商: | AM42DL6404G85IT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁

54

Am42DL6404G

March 20, 2002

P R E L I M I N A R Y

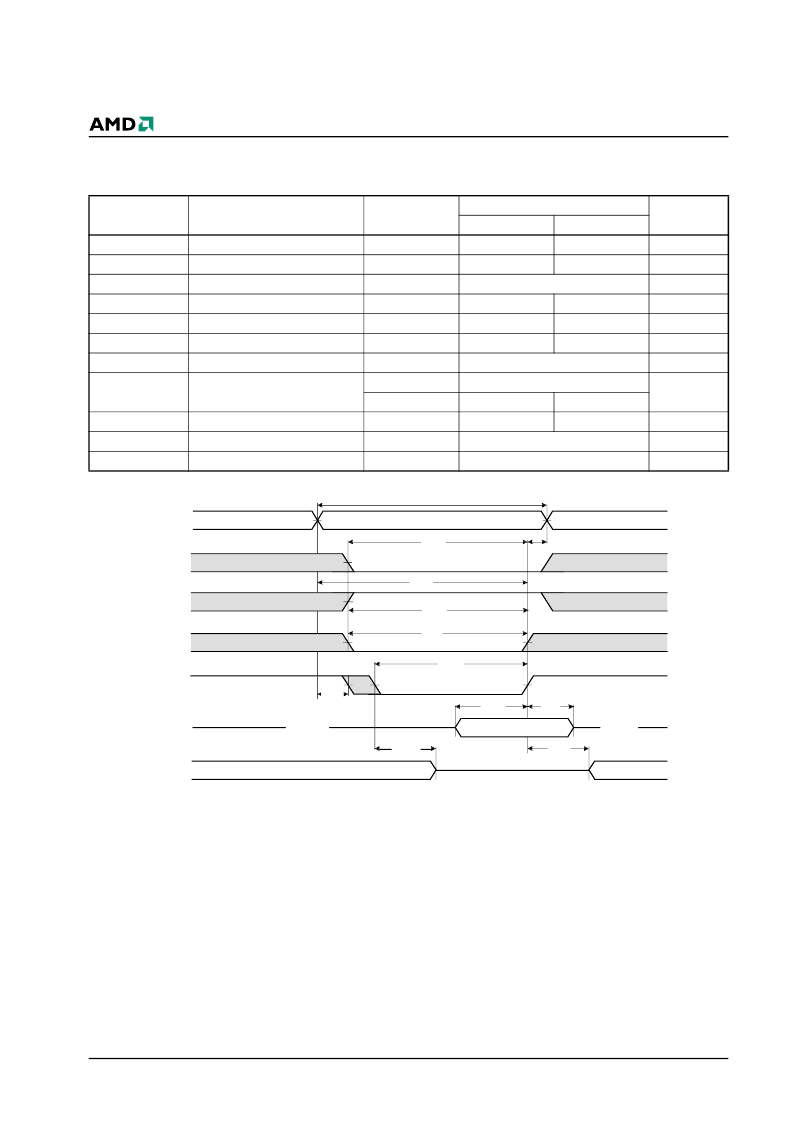

SRAM CHARACTERISTICS

Write Cycle

Notes:

1. WE# controlled.

2. t

CW

is measured from CE1#s going low to the end of write.

3. t

WR

is measured from the end of write to the address change. t

WR

applied in case a write ends as CE1#s or WE# going high.

4. t

AS

is measured from the address valid to the beginning of write.

5. A write occurs during the overlap (t

WP

) of low CE#1 and low WE#. A write begins when CE1#s goes low and WE# goes low when

asserting UB#s or LB#s for a single byte operation or simultaneously asserting UB#s and LB#s for a double byte operation. A

write ends at the earliest transition when CE1#s goes high and WE# goes high. The t

WP

is measured from the beginning of write

to the end of write.

6. If CE1# goes low (or CE2 goes high) at the same time or after WE# goes low, the outputs will remain at high impedance.

7. If CE1# goes high (or CE2 goes low) at the same time or before WE# goes high, the outputs will remain at high impedance.

8. If OE# is high during the write cycle, the outputs will remain at high impedance.

9. Output data may be present on the bus at this time; input signals should not be applied.

Figure 30.

SRAM Write Cycle

—

WE# Control

Parameter

Symbol

Description

Speed

Unit

70

85

t

WC

t

Cw

t

AS

t

AW

t

BW

t

WP

t

WR

Write Cycle Time

Min

70

85

ns

Chip Enable to End of Write

Min

60

70

ns

Address Setup Time

Min

0

ns

Address Valid to End of Write

Min

60

70

ns

UB#s, LB#s to End of Write

Min

60

70

ns

Write Pulse Time

Min

50

60

ns

Write Recovery Time

Min

0

ns

t

WHZ

Write to Output High-Z

Min

0

ns

Max

20

25

t

DW

t

DH

t

OW

Data to Write Time Overlap

Min

30

35

ns

Data Hold from Write Time

Min

0

ns

End Write to Output Low-Z

Min

5

ns

Address

CS1#s

UB#s, LB#s

WE#

Data In

Data Out

t

WC

t

CW

(See Note 2)

t

AW

High-Z

High-Z

Data Valid

CS2s

t

CW

(See Note 2)

t

BW

t

WP

(See Note 5)

t

(See Note 4)

t

WR

(See Note 3)

t

WHZ

t

DW

t

DH

t

OW

(See Note 9)

(See Note 9)

(See Note 7)

(See Note 6)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM42DL640AH70IS | 64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Static RAM |

| AM42DL640AH70IT | 64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Static RAM |

| AM42DL640AH85IS | 64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Static RAM |

| AM42DL640AH85IT | 64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Static RAM |

| AM49DL322BGB70 | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM42DL6408G70I | 制造商:Spansion 功能描述:64M (X8/X16) FLASH, 8M (X16) SRAM, 3V, FBGA73, IND - Trays |

| AM42DL640AG | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:64 Megabit (8 M x 8-Bit/4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Static RAM |

| AM42DL640AG25IT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:64 Megabit (8 M x 8-Bit/4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Static RAM |

| AM42DL640AG30IT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:64 Megabit (8 M x 8-Bit/4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Static RAM |

| AM42DL640AG35IT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:64 Megabit (8 M x 8-Bit/4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Static RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。