- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366355 > AM27C256-55DIB (ADVANCED MICRO DEVICES INC) 256 Kilobit (32 K x 8-Bit) CMOS EPRO PDF資料下載

參數(shù)資料

| 型號(hào): | AM27C256-55DIB |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | PROM |

| 英文描述: | 256 Kilobit (32 K x 8-Bit) CMOS EPRO |

| 中文描述: | 32K X 8 UVPROM, 55 ns, CDIP28 |

| 封裝: | WINDOWED, CERAMIC, DIP-28 |

| 文件頁(yè)數(shù): | 1/12頁(yè) |

| 文件大小: | 90K |

| 代理商: | AM27C256-55DIB |

Publication#

08007

Issue Date:

May 1995

Rev.

H

Amendment

/0

2-32

Advanced

Micro

Devices

Am27C256

256 Kilobit (32,768 x 8-Bit) CMOS EPROM

FINAL

DISTINCTIVE CHARACTERISTICS

I

Fast access time

—

55 ns

I

Low power consumption

—

20

μ

A typical CMOS standby current

I

JEDEC-approved pinout

I

Single +5 V power supply

I

±

10% power supply tolerance available

I

100% Flashrite programming

— Typical programming time of 4 seconds

I

Latch-up protected to 100 mA from –1 V to

V

CC

+ 1 V

I

High noise immunity

I

Versatile features for simple interfacing

— Both CMOS and TTL input/output

compatibility

— Two line control functions

I

Standard 28-pin DIP, PDIP, 32-pin TSOP and

PLCC packages

GENERAL DESCRIPTION

The Am27C256 is a 256K-bit ultraviolet erasable pro-

grammable read-only memory. It is organized as 32K

words by 8 bits per word, operates from a single +5 V

supply, has a static standby mode, and features fast sin-

gle address location programming. Products are avail-

able in windowed ceramic DIP packages as well as plas-

tic one time programmable (OTP) PDIP, TSOP, and

PLCC packages.

Typically, any byte can be accessed in less than 55 ns,

allowing operation with high-performance microproces-

sors without any WAIT states. The Am27C256 offers

separate Output Enable (

OE

) and Chip Enable (

CE

)

controls, thus eliminating bus contention in a multiple

bus microprocessor system.

AMD’s CMOS process technology provides high speed,

low power, and high noise immunity. Typical power con-

sumption is only 80 mW in active mode, and 100

μ

W in

standby mode.

All signals are TTL levels, including programming sig-

nals. Bit locations may be programmed singly, in blocks,

or at random. The Am27C256 supports AMD’s Flashrite

programming algorithm (100

μ

s pulses) resulting in typi-

cal programming time of 4 seconds.

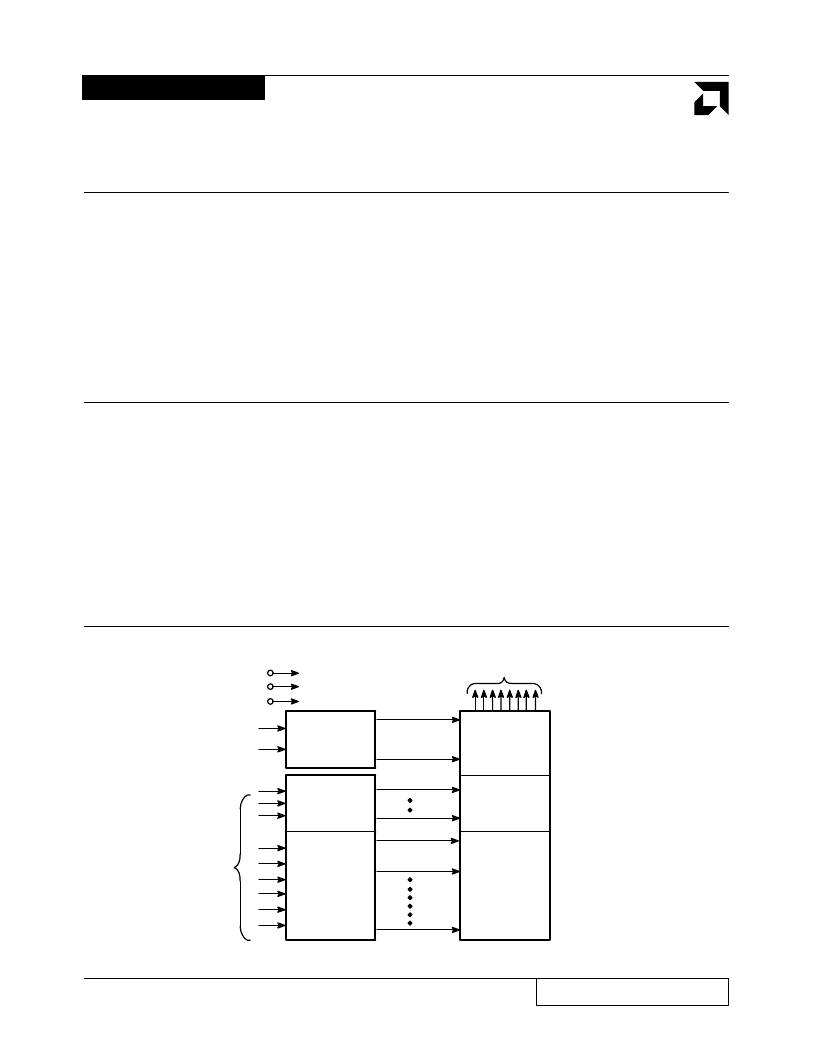

BLOCK DIAGRAM

V

CC

V

SS

V

PP

Output Enable

Chip Enable

and

Prog Logic

Y

Decoder

X

Decoder

CE

OE

Output

Buffers

Y

Gating

262,144

Bit Cell

Matrix

A0–A14

Address

Inputs

Data Outputs

DQ0–DQ7

08007H-1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM27C256-255DIB | 256 Kilobit (32 K x 8-Bit) CMOS EPRO |

| AM27C256-255JC | 256 Kilobit (32,768 x 8-Bit) CMOS EPROM |

| AM27C256 | Quadruple 2-Input Multiplexers With Storage 16-SOIC 0 to 70 |

| AM27C256-200EI | 256 Kilobit (32,768 x 8-Bit) CMOS EPROM |

| AM27C256-200JC | 256 Kilobit (32 K x 8-Bit) CMOS EPRO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM27C25655JC | 制造商:AMD 功能描述:* |

| AM27C256-55PC | 制造商:Rochester Electronics LLC 功能描述: |

| AM27C25670JC | 制造商:AMD 功能描述:New |

| AM27C256-90DI | 制造商:Rochester Electronics LLC 功能描述: |

| AM27C256-90JC | 制造商:Advanced Micro Devices 功能描述:EPROM, 32K x 8, 32 Pin, Plastic, PLCC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。