- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374046 > ADV7181BBCPZ (ANALOG DEVICES INC) Multiformat SDTV Video Decoder PDF資料下載

參數(shù)資料

| 型號: | ADV7181BBCPZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | Multiformat SDTV Video Decoder |

| 中文描述: | COLOR SIGNAL DECODER, QCC64 |

| 封裝: | 9 X 9 MM, LEAD FREE, MO-220-VMMD, LFCSP-64 |

| 文件頁數(shù): | 83/96頁 |

| 文件大?。?/td> | 873K |

| 代理商: | ADV7181BBCPZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁當(dāng)前第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

ADV7181B

Rev. 0 | Page 83 of 96

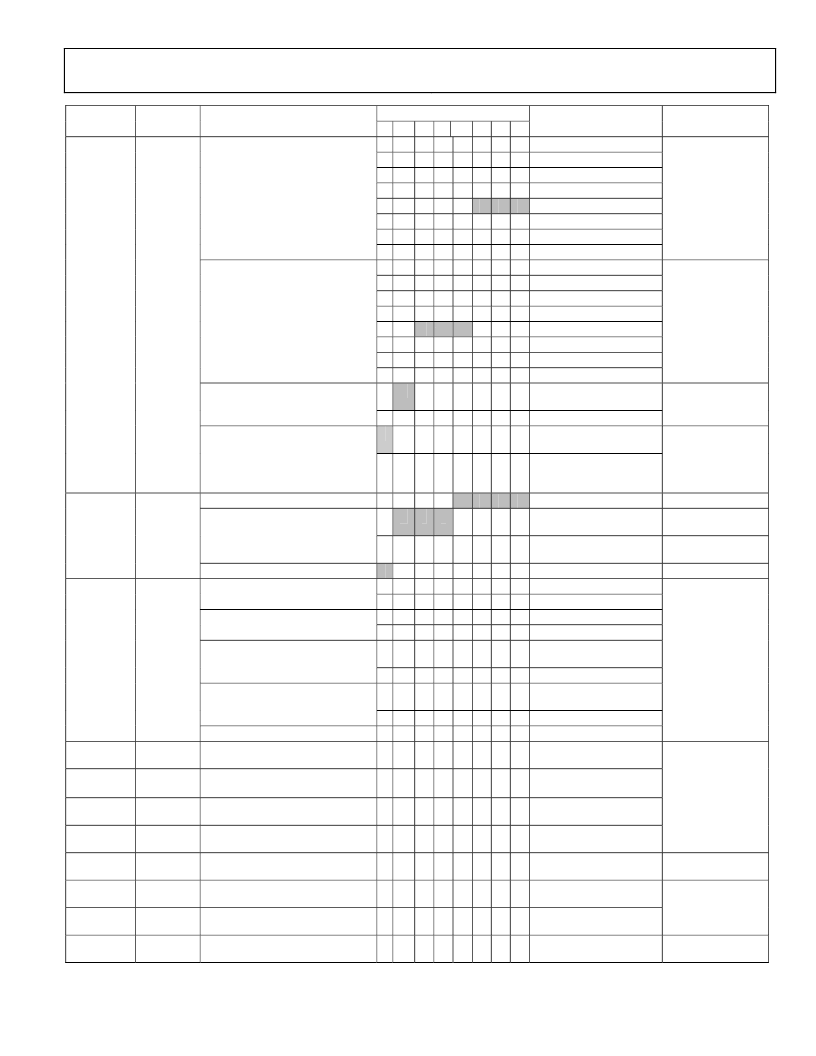

Bits

4

0

0

1

1

0

0

1

1

Subaddress

0x51

Register

Lock Count

Bit Description

CIL[2:0]. Count-into-lock determines

the number of lines the system must

remain in lock before showing a

locked status.

7

6

0

5

0

0

0

0

1

1

1

1

3

0

1

0

1

0

1

0

1

2

0

0

0

0

1

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

Comments

1 line of video

2 lines of video

5 lines of video

10 lines of video

100 lines of video

500 lines of video

1000 lines of video

100000 lines of video

1 line of video

2 lines of video

5 lines of video

10 lines of video

100 lines of video

500 lines of video

1000 lines of video

100000 lines of video

Over field with vertical

info

Line-to-line evaluation

Lock status set only by

horizontal lock

Lock status set by

horizontal lock and

subcarrier lock.

Set to default

LLC1 (nominal 27 MHz)

selected out on LLC1 pin

LLC2 (nominally 13.5 MHz)

selected out on LLC1 pin

Set to default

No WSS detected

WSS detected

No CCAP signals detected

CCAP sequence detected

No EDTV sequence

detected

EDTV sequence detected

No CGMS transition

detected

CGMS sequence decoded

Notes

COL[2:0]. Count-out-of-lock

determines the number of lines the

system must remain out-of-lock

before showing a lost-locked status.

SRLS. Select raw lock signal. Selects

the determination of the lock.

Status.

0

1

FSCLE. Fsc lock enable.

1

Reserved

LLC_PAD_SEL [2:0]. Enables manual

selection of clock for LLC1 pin.

0

0

0

0

0

0

0

1

0

1

For 16-bit 4:2:2 out,

OF_SEL[3:0] = 0010

Read-only status

bits

0x8F

Free Run

Line

Length 1

Reserved

WSSD. Screen signaling detected.

0

0

0

1

0

1

CCAPD. Closed caption data.

EDTVD. EDTV sequence

0

1

CGMSD. CGMS sequence

x

x

x

x

x

x

x

x

1

x

x

x

x

0x90

VBI Info

(Read

Only)

Reserved

WSS1[7:0]

Wide screen signaling data.

WSS2[7:0]

Wide screen signaling data.

EDTV1[7:0]

EDTV data register.

EDTV2[7:0]

EDTV data register.

EDTV3[7:0]

EDTV data register.

CGMS1[7:0]

CGMS data register.

CGMS2[7:0]

CGMS data register.

CGMS3[7:0]

CGMS data register.

0x91

WSS1

(Read Only)

WSS2

(Read Only)

EDTV1

(Read Only)

EDTV2

(Read Only)

EDTV3

(Read Only)

CGMS1

(Read Only)

CGMS2

(Read Only)

CGMS3

(Read Only)

0x92

x

x

x

x

x

x

x

x

WSS2[7:6] are

undetermined

0x93

x

x

x

x

x

x

x

x

0x94

x

x

x

x

x

x

x

x

0x95

x

x

x

x

x

x

x

x

EDTV3[7:6] are

undetermined

EDTV3[5] is reserved

for future use

0x96

x

x

x

x

x

x

x

x

0x97

x

x

x

x

x

x

x

x

0x98

x

x

x

x

x

x

x

x

CGMS3[7:4] are

undetermined

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7181BBSTZ | Multiformat SDTV Video Decoder |

| ADV7181BCP | Multiformat SDTV Video Decoder |

| ADV7181BST | Multiformat SDTV Video Decoder |

| ADV7183B | Multiformat SDTV Video Decoder |

| ADV7183BBSTZ | Multiformat SDTV Video Decoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7181BBSTZ | 制造商:Analog Devices 功能描述:Video Decoder 3ADC 9-Bit 64-Pin LQFP 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7181BCP | 制造商:Analog Devices 功能描述:Video Decoder 3ADC 9-Bit 64-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:10BIT NTSC/PAL/SECAM VIDEO DECODER I.C. - Bulk |

| ADV7181BCPZ | 制造商:Analog Devices 功能描述: |

| ADV7181BST | 制造商:Analog Devices 功能描述:Video Decoder 3ADC 9-Bit 64-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:9-BIT BIT NTSC/PAL/SECAM VIDEO DECODER - Bulk 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7181C | 制造商:AD 制造商全稱:Analog Devices 功能描述:10-Bit, Integrated, Multiformat SDTV Video Decoder and RGB Graphics Digitizer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。