- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD664TD-UNI (ANALOG DEVICES INC) Monolithic 12-Bit Quad DAC PDF資料下載

參數(shù)資料

| 型號(hào): | AD664TD-UNI |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | Monolithic 12-Bit Quad DAC |

| 中文描述: | QUAD, PARALLEL, WORD INPUT LOADING, 10 us SETTLING TIME, 12-BIT DAC, CDIP28 |

| 封裝: | HERMETIC SEALED, CERAMIC, DIP-28 |

| 文件頁(yè)數(shù): | 12/20頁(yè) |

| 文件大小: | 566K |

| 代理商: | AD664TD-UNI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

AD664

REV. C

–12–

Output Loads

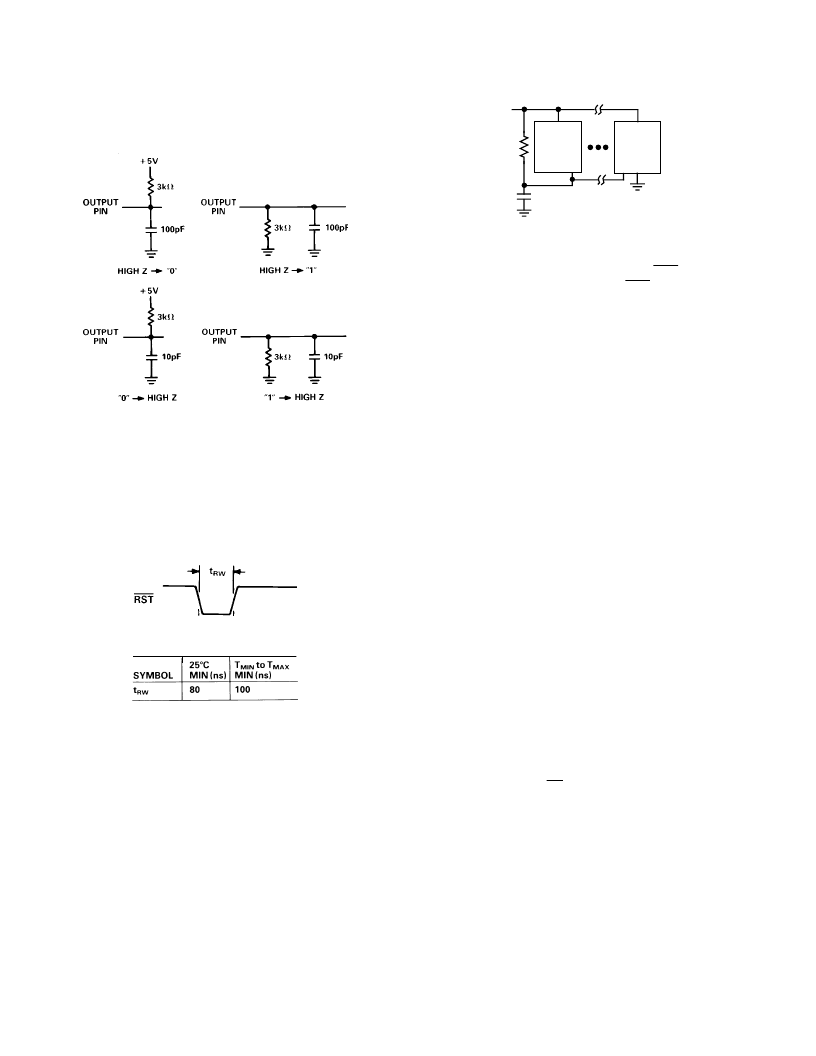

Readback timing is tested with the output loads shown in Figure

22.

Figure 22. Output Loads

Asynchronous Reset Operation

The asynchronous reset signal shown in Figure 23 may be

asserted at any time. A minimum pulse width (t

RW

) of 90 ns is

required. The reset feature is designed to return all DAC out-

puts to 0 volts regardless of the mode or range selected. In the

44-pin versions, the modes are reset to unipolar 10 V span (gain

of 1), and the input codes are rewritten to be “0s.” Previous

DAC code and mode information is erased.

Figure 23a. Asynchronous Reset Operation

Figure 23b. Asynchronous Reset Operation Timing

In the 28-pin versions of the AD664, the mode remains

unchanged, the appropriate input code is rewritten to reset the

output voltage to 0 volts. As in the 44-pin versions, the previous

input data is erased.

At power-up, an AD664 may be activated in either the read or

write modes. While at the device level this will not produce any

problems, at the system level it may. Analog Devices recom-

mends the addition of a simple power-on reset scheme to any

system where the possibility of an unknown start-up state could

be a problem. The simplest version of this scheme is illustrated

in Figure 24.

AD664

#1

AD664

#N

+5V

10k

100nF

RST

RST

Figure 24. Power-On Reset

It is obvious from inspection that the scheme shown in Figure

24 is only appropriate for systems in which the

RST

is otherwise

not used. Should the user wish to use the

RST

pin, an addi-

tional logic gate may be included to combine the power-on reset

with the reset signal.

INTERFACING THE AD664 TO MICROPROCESSORS

The AD664 is easy to interface with a wide variety of popular

microprocessors. Common architectures include processors with

dedicated 8-bit data and address buses, an 8-bit bus over which

data and address are multiplexed, an 8-bit data and 16-bit

address partially muxed, and separate 16-bit data and address

buses.

AD664 addressing can be accomplished through either

memory-mapped or I/O techniques. In memory-mapped

schemes, the AD664 appears to the host microprocessor as

RAM memory. Standard memory addressing techniques are

used to select the AD664. In the I/O schemes, the AD664 is

treated as an external I/O device by the host. Dedicated I/O pins

are used to address the AD664.

MC6801 Interface

In Figures 25a–25d, we illustrate a few of the various methods

that can be used to connect an AD664 to the popular MC6801

microprocessor. In each of these cases, the MC6801 is intended

to be configured in its expanded, nonmultiplexed mode of

operation. In this mode, the MC6801 can address 256 bytes of

external memory over 8-bit data (Port 3) and 8-bit address

(Port 4) buses. Eight general-purpose I/O lines (Port 1) are also

available. On-board RAM and ROM provide program and data

storage space.

In Figure 25a, the three least significant address bits (P40, P41

and P42) are employed to select the appropriate on-chip

addresses for the various input registers of the AD664. Three

I/O lines (P17, P16 and P15) are used to select various operat-

ing features of the the AD664. IOS and E(nable) are combined

to produce an appropriate

CS

signal. This addressing scheme

leaves the five most significant address bits and five I/O lines

free for other tasks in the system.

Figure 25b shows another way to interface an AD664 to the

MC6801. Here we’ve used the six least significant address lines

to select AD664 features and registers. This is a purely memory-

mapped scheme while the one illustrated in Figure 25a uses

some memory-mapping as well as some dedicated I/O pins. In

Figure 25b, two address lines and all eight I/O lines remain free

for other system tasks.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD664AJ | Monolithic 12-Bit Quad DAC |

| AD664BE | Monolithic 12-Bit Quad DAC |

| AD664BJ | Monolithic 12-Bit Quad DAC |

| AD664KP | Monolithic 12-Bit Quad DAC |

| AD664 | Monolithic 12-Bit Quad DAC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD664TD-UNI/883B | 制造商:Analog Devices 功能描述:DAC 4-CH R-2R 12-bit 28-Pin CDIP Tube 制造商:Analog Devices 功能描述:DAC 4-CH R-2R 12-BIT 28CDIP - Rail/Tube 制造商:Analog Devices Inc. 功能描述:Digital to Analog Converters - DAC IC MONO 12-BIT QUAD 制造商:Analog Devices 功能描述:CONVERTER - DAC |

| AD664TE/883B | 功能描述:數(shù)模轉(zhuǎn)換器- DAC IC - 12-BIT DACPORT IC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| AD664TJ/883B | 功能描述:數(shù)模轉(zhuǎn)換器- DAC IC - 12-BIT QUAD DAC IC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| AD664XFFA | 制造商:Analog Devices 功能描述:IC, MONO QUAD 12-BIT DAC - Bulk |

| AD6650 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Diversity IF to Baseband GSM/EDGE Narrowband Receiver |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。