- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373859 > AD1819A (Analog Devices, Inc.) AC97 SoundPort Codec(AC97型聲音端口信號(hào)編解碼器) PDF資料下載

參數(shù)資料

| 型號(hào): | AD1819A |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | Codec |

| 英文描述: | AC97 SoundPort Codec(AC97型聲音端口信號(hào)編解碼器) |

| 中文描述: | AC97 SoundPort編解碼器(AC97型聲音端口信號(hào)編解碼器) |

| 文件頁數(shù): | 20/28頁 |

| 文件大?。?/td> | 265K |

| 代理商: | AD1819A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AD1819A

–20–

REV. 0

VALID

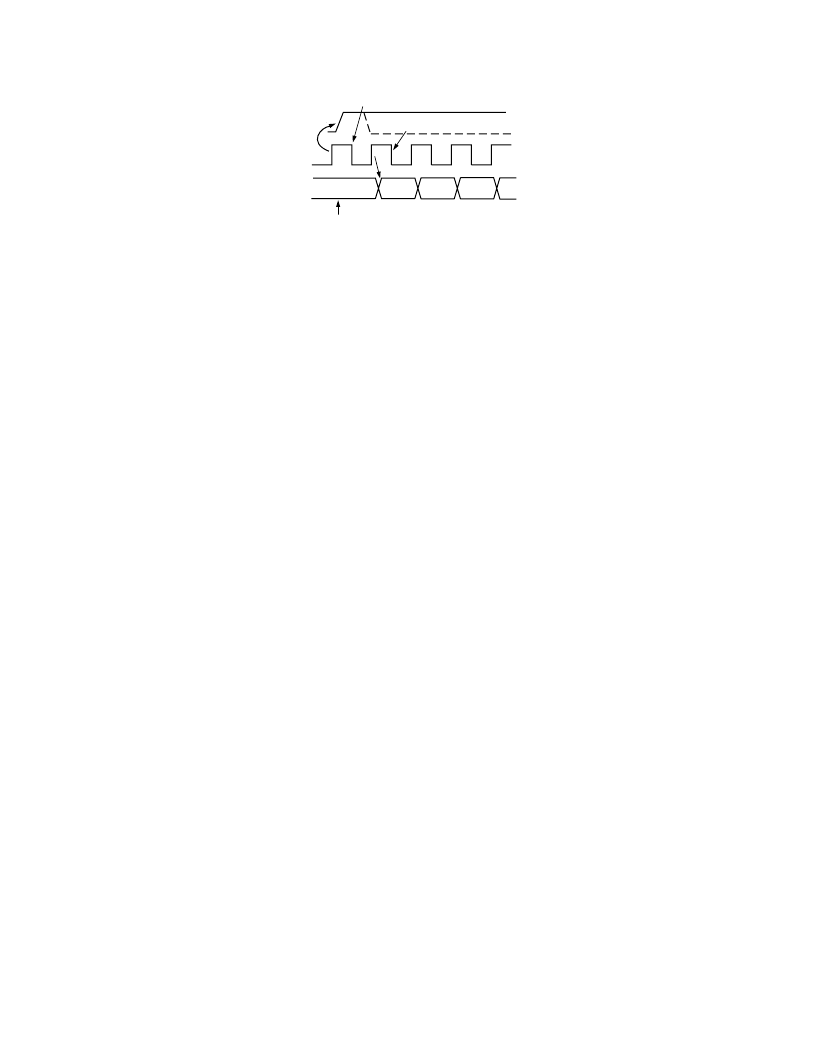

FRAME

SLOT (1) SLOT (2)

AC ’97 CONTROLLER SAMPLES

FIRST SDATA_OUT BIT OF FRAME HERE

SYNC

BIT_CLK

SDATA_OUT

AD1819A SAMPLES SYNC ASSERTION HERE

END OF PREVIOUS

AUDIO FRAME

Figure 11. Start of an Audio Output Frame

SDAT A_OUT ’s composite stream is MSB justified (MSB first) with all nonvalid slots’ bit positions stuffed with 0s by the

AC ’97 controller. T he AD1819A ignores invalid slots.

In the event that there are less than 20 valid bits within an assigned and valid time slot, the AC ’97 controller always stuffs all trailing

nonvalid bit positions of the 20-bit slot with 0s. T he AD1819A ignores unused bits.

As an example, consider an 8-bit sample stream being played out to one of the AD1819A’s DACs. T he first 8-bit positions are pre-

sented to the DAC (MSB justified), followed by the next 12 bit positions, which are stuffed with 0s by the AC ’97 controller.

When mono audio sample streams are output from the AC ’97 controller, it is necessary that BOT H left and right stream time slots

be filled with the same data.

Slot 1: Command Address Port

T he command port is used to control features and request status (see Audio Input Frame Slots l and 2) for AD1819A functions

including, but not limited to, mixer settings and power management (refer to the control register section of this specification).

T he control interface architecture supports up to sixty-four 16-bit read/write registers, addressable on even byte boundaries. Only the

even registers (00h, 02h, etc.) are valid, odd register (01h, 03h, etc.) accesses are discouraged (defaulting to the preceding even byte

boundary—i.e., a read to 01h will return the 16-bit contents of 00h). Note that shadowing of the control register file on the AC ’97

controller is an option left open to the implementation of the AC ’97 controller. T he AD1819A’s control register file is readable as

well as writable.

Audio output frame Slot 1 communicates control register address, and write/read command information to AD1819A.

Command Address Port Bit Assignments:

Bit (19)

Bit (18:12)

Bit (11:0)

T he first bit (MSB) sampled by the AD1819A indicates whether the current control transaction is a read or a write operation. T he

following 7-bit positions communicate the targeted control register address. T he trailing 12-bit positions within the slot are reserved.

Read/Write Command

Control Register Index

Reserved

(1 = Read, 0 = Write)

(64 16-Bit Locations, Addressed On Even Byte Boundaries)

(Stuffed with 0s)

Slot 2: Command Data Port

T he command data port is used to deliver 16-bit control register write data in the event that the current command port operation is a

write cycle (as indicated by Slot 1, Bit 19).

Bit (19:4)

Control Register Write Data

(Stuffed with 0s If Current Operation Is Not a Write)

Bit (3:0)

Reserved

(Stuffed with 0s)

If the current command port operation is not a write, the entire slot time should be stuffed with 0s by the AC ’97 controller.

Slot 3: PCM Playback Left Channel

Audio output frame Slot 3 is the composite digital audio left playback stream. In a typical “Games Compatible” PC this slot is com-

posed of standard PCM (.wav) output samples digitally mixed (on the AC ’97 controller or host processor) with music synthesis

output samples. If a sample stream of resolution less than 20 bits is transferred, the AC ’97 controller should stuff all trailing

nonvalid bit positions within this time slot with 0s.

Slot 4: PCM Playback Right Channel

Audio output frame Slot 4 is the composite digital audio right playback stream. In a typical “Games Compatible” PC this slot is

composed of standard PCM (.wav) output samples digitally mixed (on the AC ’97 controller or host processor) with music synthesis

output samples. If a sample stream of resolution less than 20 bits is transferred, the AC ’97 controller should stuff all trailing nonvalid bit

positions within this time slot with 0s.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1819BJST | AC’97 SoundPort Codec |

| AD1819 | ECONOLINE: RD & RC - Dual Output from a Single Input Rail- 1kVDC & 2kVDC Isolation- Power Sharing on Output- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 86% |

| AD1819B | AC’97 SoundPort Codec |

| AD1833A | 24-Bit, 192 kHz, DAC |

| AD1833AAST | ECONOLINE: RD & RC - Dual Output from a Single Input Rail- 1kVDC & 2kVDC Isolation- Power Sharing on Output- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 86% |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD1819AJST | 制造商:Rochester Electronics LLC 功能描述: |

| AD1819B | 制造商:AD 制造商全稱:Analog Devices 功能描述:AC’97 SoundPort Codec |

| AD1819BJST | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 48-Pin LQFP 制造商:Analog Devices 功能描述:IC CODEC AC'97 VERSION 2.1 |

| AD1819BJST-REEL | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 48-Pin LQFP T/R |

| AD1819BJSTZ | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 48-Pin LQFP 制造商:Analog Devices 功能描述:Audio CODEC IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。