- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4457 > A1020B-PLG68C (Microsemi SoC)IC FPGA 2K GATES 68-PLCC COM PDF資料下載

參數(shù)資料

| 型號: | A1020B-PLG68C |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 37/98頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 2K GATES 68-PLCC COM |

| 標(biāo)準(zhǔn)包裝: | 19 |

| 系列: | ACT™ 1 |

| LAB/CLB數(shù): | 547 |

| 輸入/輸出數(shù): | 57 |

| 門數(shù): | 2000 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 68-PLCC(24.23x24.23) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

42

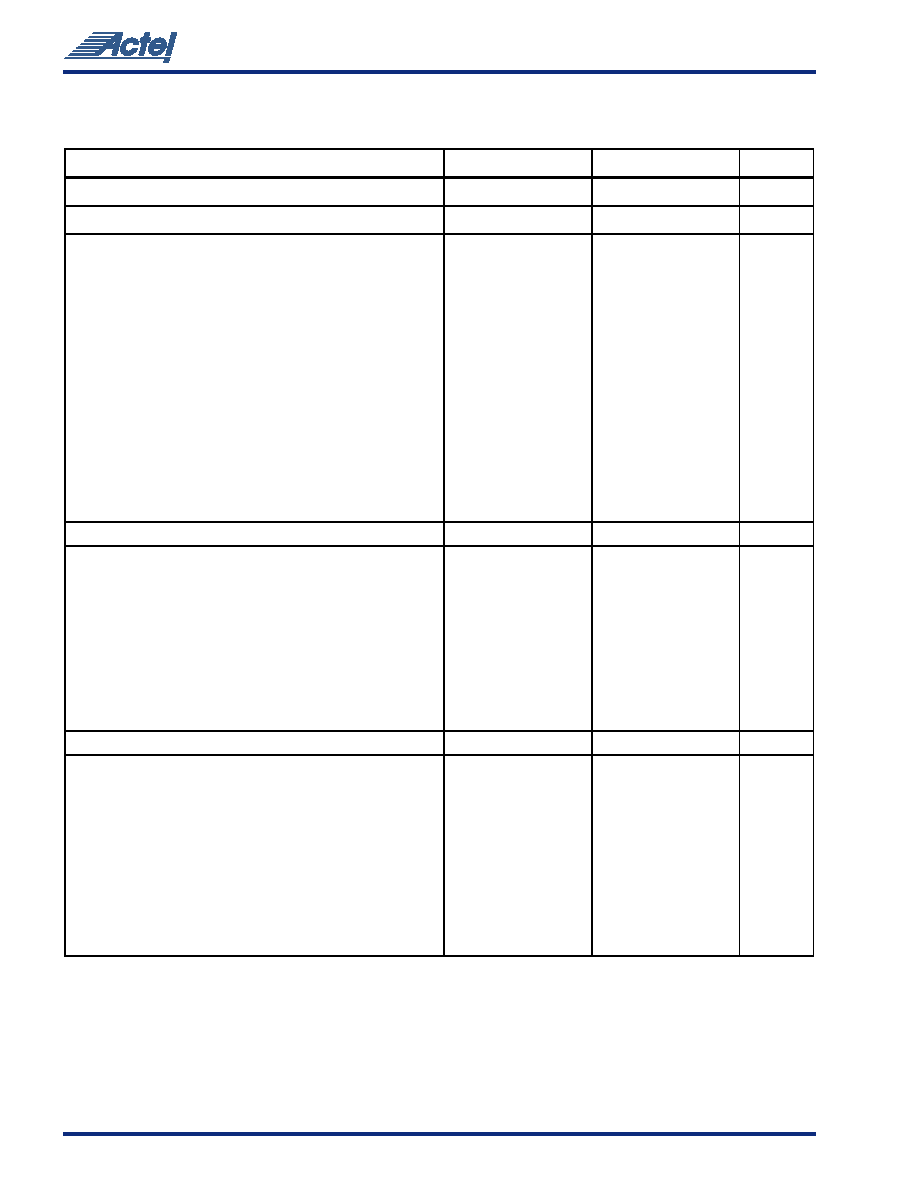

A1 46 0A T i m i n g C har a c t e r i st i c s (continued)

(W or s t - C as e M i l i t a r y Cond i t i o n s , V CC = 4.5 V, TJ = 1 25°C)

‘–1’ Speed

‘Std’ Speed

Parameter

Description

Min.

Max.

Min.

Max.

Units

CMOS Output Module Timing1

tDHS

Data to Pad, High Slew

9.2

10.8

ns

tDLS

Data to Pad, Low Slew

17.3

20.3

ns

tENZHS

Enable to Pad, Z to H/L, High Slew

7.7

9.1

ns

tENZLS

Enable to Pad, Z to H/L, Low Slew

13.1

15.5

ns

tENHSZ

Enable to Pad, H/L to Z, High Slew

10.9

12.8

ns

tENLSZ

Enable to Pad, H/L to Z, Low Slew

10.9

12.8

ns

tCKHS

IOCLK Pad to Pad H/L, High Slew

14.1

16.0

ns

tCKLS

IOCLK Pad to Pad H/L, Low Slew

20.2

22.4

ns

dTLHHS

Delta Low to High, High Slew

0.06

0.07

ns/pF

dTLHLS

Delta Low to High, Low Slew

0.11

0.13

ns/pF

dTHLHS

Delta High to Low, High Slew

0.04

0.05

ns/pF

dTHLLS

Delta High to Low, Low Slew

0.05

0.06

ns/pF

Dedicated (Hard-Wired) I/O Clock Network

tIOCKH

Input Low to High

(Pad to I/O Module Input)

3.5

4.1

ns

tIOPWH

Minimum Pulse Width High

4.8

5.7

ns

tIOPWL

Minimum Pulse Width Low

4.8

5.7

ns

tIOSAPW

Minimum Asynchronous Pulse Width

3.9

4.4

ns

tIOCKSW

Maximum Skew

0.9

1.0

ns

tIOP

Minimum Period

9.9

11.6

ns

fIOMAX

Maximum Frequency

100

85

MHz

Dedicated (Hard-Wired) Array Clock Network

tHCKH

Input Low to High

(Pad to S-Module Input)

5.5

6.4

ns

tHCKL

Input High to Low

(Pad to S-Module Input)

5.5

6.4

ns

tHPWH

Minimum Pulse Width High

4.8

5.7

ns

tHPWL

Minimum Pulse Width Low

4.8

5.7

ns

tHCKSW

Maximum Skew

0.9

1.0

ns

tHP

Minimum Period

9.9

11.6

ns

fHMAX

Maximum Frequency

100

85

MHz

Notes:

1.

Delays based on 35 pF loading.

2.

SSO information can be found in the Simultaneously Switching Output Limits for Actel FPGAs application note at

http://www.actel.com/appnotes.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RSC30DTEI | CONN EDGECARD 60POS .100 EYELET |

| HMC49DRTI | CONN EDGECARD 98POS DIP .100 SLD |

| HMC49DREI | CONN EDGECARD 98POS .100 EYELET |

| A3PE600-2PQG208I | IC FPGA 600000 GATES 208-PQFP |

| 4-552008-1 | CONN CHAMP COVER 50 POS 180 DEG |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A1020B-PLG68I | 功能描述:IC FPGA 2K GATES 68-PLCC IND RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A1020B-PLG84C | 功能描述:IC FPGA 2K GATES 84-PLCC COM RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A1020B-PLG84I | 功能描述:IC FPGA 2K GATES 84-PLCC IND RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A1020B-PLG84M | 制造商:Microsemi Corporation 功能描述:FPGA ACT 1 Family 2K Gates 547 Cells 48MHz 1.0um Technology 5V 84-Pin PLCC 制造商:Microsemi Corporation 功能描述:FPGA ACT 1 2K GATES 547 CELLS 48MHZ 1.0UM 5V 84PLCC - Rail/Tube 制造商:Microsemi Corporation 功能描述:IC FPGA 2K GATES 84-PLCC MIL |

| A1020B-PQ100C | 功能描述:IC FPGA 2K GATES 100-PQFP COM RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。