- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360656 > 9S12DP512DGV1 9S12Dx512 Device Guide PDF資料下載

參數(shù)資料

| 型號: | 9S12DP512DGV1 |

| 英文描述: | 9S12Dx512 Device Guide |

| 中文描述: | 9S12Dx512設備指南 |

| 文件頁數(shù): | 2/126頁 |

| 文件大?。?/td> | 1809K |

| 代理商: | 9S12DP512DGV1 |

第1頁當前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

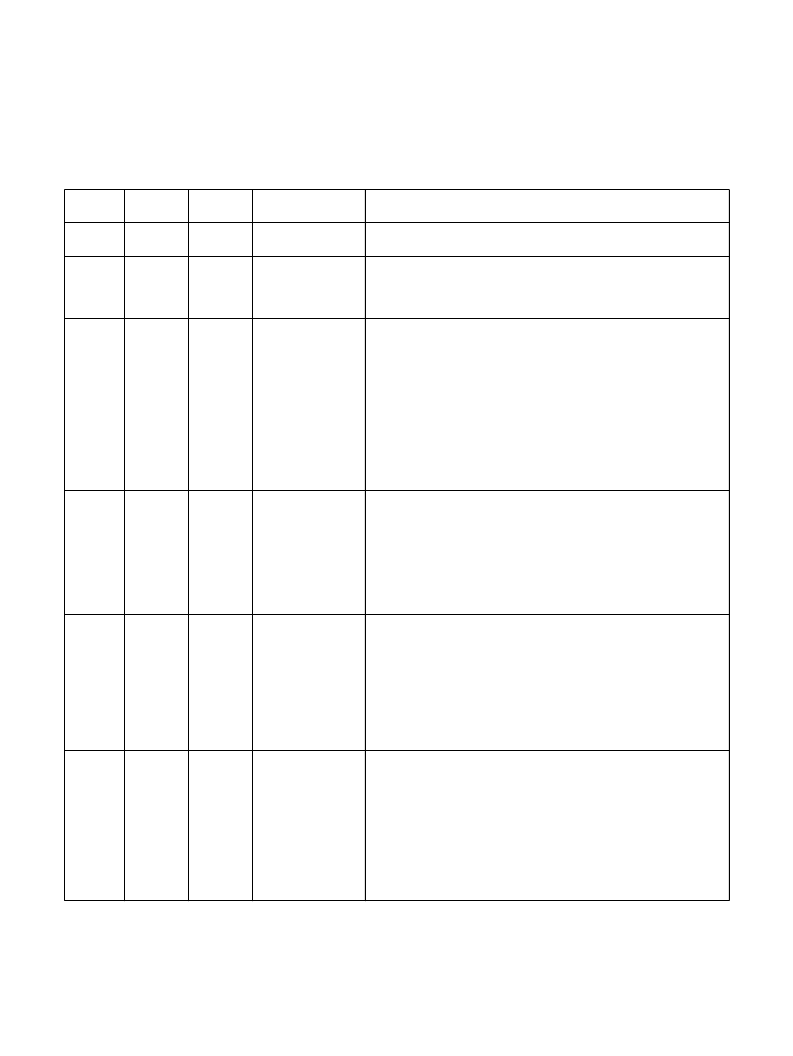

Revision History

Version

Number

Revision

Date

16 NOV

2001

Effective

Date

19 NOV

2001

Author

Description of Changes

V01.00

Initial version based on MC9SDP256-2.09 Version.

V01.01

18 FEB

2002

18 FEB

2002

In table 7 I/O Characteristics" of the electrical characteristics

replaced tPULSE with tpign and tpval in lines "Port ... Interrupt Input

Pulse filtered" and "Port ... Interrupt Input Pulse passed"

respectively.

Table "Oscillator Characteristics": removed "Oscillator start-up time

from POR or STOP" row

Table "5V I/O Characteristics": Updated

Partial Drive IOH = +–2mA and Full Drive IOH = –10mA

Table "ATD Operating Characteristics": Distinguish I

REF

for 1 and 2

ATD blocks on

Table "ATD Electrical Characteristics": Update C

INS

to 22 pF

Table "Operating Conditions": Changed V

DD

and V

DDPLL

to 2.35 V

(min)

Removed Document number except from Cover Sheet

Updated Table "Document References"

Table "5V I/O Characteristics" : Corrected Input Capacitance to 6pF

Section: "Device Pinout" (112-pin and 80-pin): added in diagrams

RXCAN0 to PJ6 and TXCAN0 to PJ7

Table "PLL Characteristics": Updated parameters K

1

and f

1

Figure "Basic PLL functional diagram": Inserted XFC pin in diagram

Enhanced section "XFC Component Selection"

Added to Sections ATD, ECT and PWM: freeze mode = active BDM

mode

Added 1L86D to Table "Assigned Part ID numbers"

Corrected MEMSIZ1 value in Table "Memory size registers"

Subsection "Device Memory Map: Removed Flash mapping from

$0000 to $3FFF.

Table "Signal Properties": Added column "Internal Pull Resistor".

Preface Table "Document References": Changed to full naming for

each block.

Table "Interrupt Vector Locations", Column "Local Enable":

Corrected several register and bit names.

Figure "Recommended PCB Layout for 80QFP: Corrected

VREGEN pin position

Thermal values for junction to board and package

BGND pin pull-up

Part Order Information

Global Register Table

Chip Configuration Summary

Modified mode of Operations chapter

Section "Printed Circuit Board Layout Proposals": added Pierce

Oscillator examples for 112LQFP and 80QFP

V01.02

6 MAR

2002

6 MAR

2002

V01.03

4 June

2002

4 June

2002

V01.04

4 July

2002

4 July

2002

V01.05

30 July

2002

30 July

2002

相關PDF資料 |

PDF描述 |

|---|---|

| 9S12DT128BDGV1 | 9S12DT128B Device Guide |

| 9S12DT128DGV2 | MC9S12DT128 Device User Guide V02.09 |

| 9S12DT128DGV2D | MC9S12DT128 Device User Guide V02.09 |

| 9S12DT256DGV3 | MC9S12DT256 Device User Guide V03.03 |

| 9S12E128DGV1 | MC9S12E-Family Device User Guide V01.04 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 9S12DT128BDGV1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:9S12DT128B Device Guide |

| 9S12DT128DGV2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MC9S12DT128 Device User Guide V02.09 |

| 9S12DT128DGV2D | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MC9S12DT128 Device User Guide V02.09 |

| 9S12DT256DGV3 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MC9S12DT256 Device User Guide V03.03 |

| 9S12E128DGV1 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MC9S12E-Family Device User Guide V01.04 |

發(fā)布緊急采購,3分鐘左右您將得到回復。