- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25565 > 9EX21501AKILF (INTEGRATED DEVICE TECHNOLOGY INC) 21501 SERIES, PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC64 PDF資料下載

參數(shù)資料

| 型號(hào): | 9EX21501AKILF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 21501 SERIES, PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC64 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MLF-64 |

| 文件頁(yè)數(shù): | 14/15頁(yè) |

| 文件大小: | 200K |

| 代理商: | 9EX21501AKILF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)

IDT

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

1578—01/18/11

9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

8

Datasheet

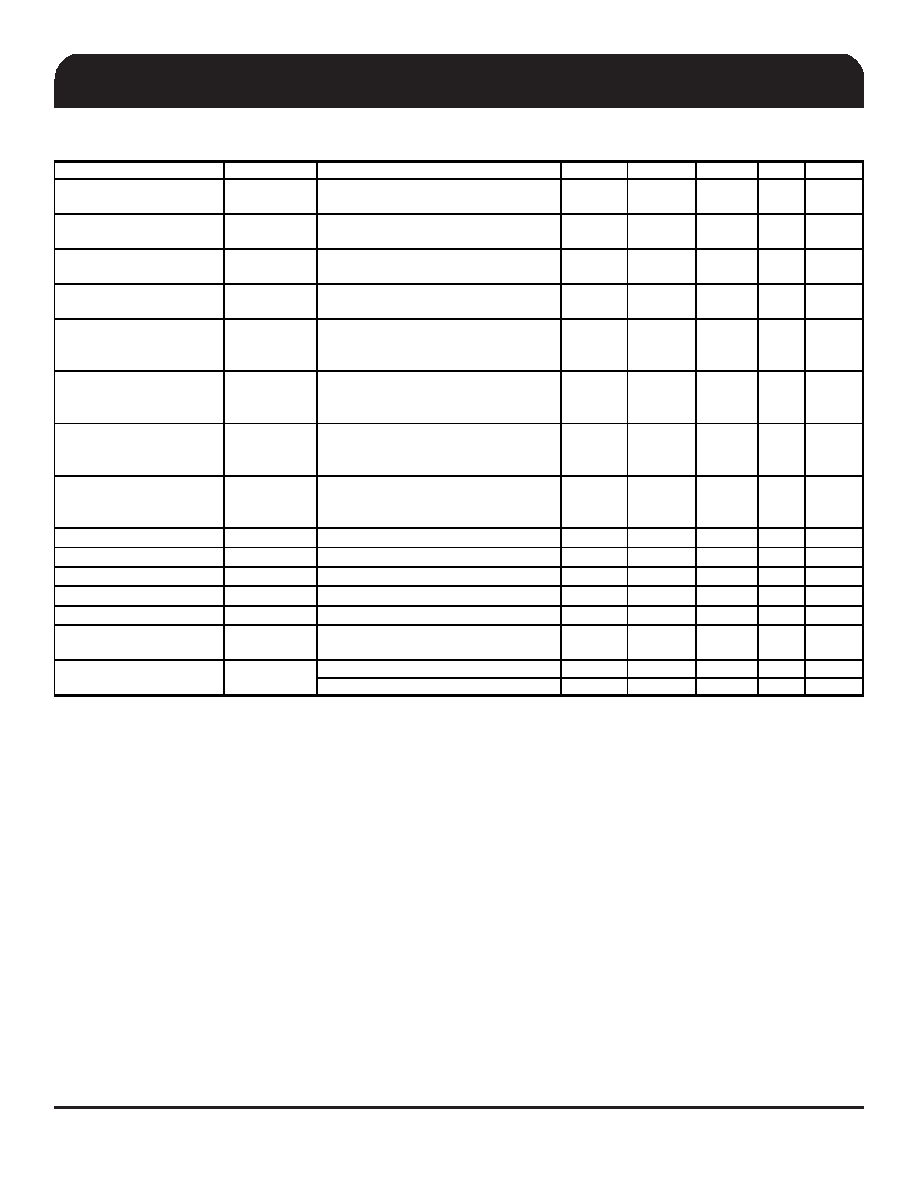

Electrical Characteristics - Skew and Differential Jitter Parameters

TA = TCOM or TIND; Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

CLK_IN, DIF[x:0], 100M

tSPO_PLL100M

Input-to-Output Skew in PLL mode

nominal value @ 25°C, 3.3V

925

1019

1125

ps

1,2,4,5,8

CLK_IN, DIF[x:0], 133M

tSPO_PLL133M

Input-to-Output Skew in PLL mode

nominal value @ 25°C, 3.3V

1100

1120

1200

ps

1,2,4,5,8

CLK_IN, DIF[x:0]

tPD_BYP

Input-to-Output Skew in Bypass mode

nominal value @ 25°C, 3.3V

4

4.6

5.2

ns

1,2,3,5,8

CLK_IN, DIF[x:0]

tDSPO_PLL

Input-to-Output Skew Varation in PLL

mode across voltage and temperature

|258|

|350|

ps

1,2,3,5,6

,8

CLK_IN, DIF[x:0]

tDSPO_BYP

Input-to-Output Skew Varation in

Bypass mode across voltage and

temperature

|771|

|900|

ps

1,2,3,5,6

,8

CLK_IN, DIF[x:0]

tDTE

Random Differential Tracking error

beween two 9EX2 devices in Hi BW

Mode

210

ps

(rms)

1,2,3,5,8

,12

CLK_IN, DIF[x:0]

tDSSTE

Random Differential Spread Spectrum

Tracking error beween two 9EX2

devices in Hi BW Mode

20

75

ps

1,2,3,5,8

,13

DIF{x:0]

tSKEW_ALL

Output-to-Output Skew

across all outputs

(Common to Bypass and PLL mode)

75

150

ps

1,2,8

PLL Jitter Peaking

jpeak-hibw

High Bandwidth

0

2.3

3

dB

7,8

PLL Jitter Peaking

jpeak-lobw

Low Bandwidth

0

2.5

3

dB

7,8

PLL Bandwidth

pllHIBW

High Bandwidth

2

2.5

4

MHz

8,9

PLL Bandwidth

pllLOBW

Low Bandwidth

0.7

0.87

1.4

MHz

8,9

Duty Cycle

tDC

Measured differentially, PLL Mode

45

49.6

55

%

1

Duty Cycle Distortion

tDCD

Measured differentially, Bypass Mode

@100MHz

-2

0.2

2

%

1,10

PLL mode

27

50

ps

1

Additive Jitter in Bypass Mode

20

50

ps

1

Notes for preceding table:

7 Measured as maximum pass band gain. At frequencies within the loop BW, highest point of magnification is called PLL jitter peaking.

8. Guaranteed by design and characterization, not 100% tested in production.

9 Measured at 3 db down or half power point.

10 Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mod

11 Measured from differential waveform

13 Differential spread spectrum tracking error is the difference in spread spectrum tracking between two ICS9EX21501 devices This

parameter is measured at the outputs of two separate ICS9EX21501 devices driven by a single CK410B+ in Spread Spectrum mode.

The ICS9EX21501's must be set to high bandwidth. The spread spectrum characteristics are: maximum of 0.5%, 30-33KHz

modulation frequency, triangle profile.

6. Long-term variation from nominal of input-to-output skew over temperature and voltage for a single device.

12. This parameter is measured at the outputs of two separate ICS9EX21501 devices driven by a single CK410B+. The

ICS9EX21501's must be set to high bandwidth. Differential phase jitter is the accumulation of the phase jitter not shared by the outputs

(eg. not including the affects of spread spectrum). Target ranges of consideration are agents with BW of 1-22Mhz and 11-33Mhz.

Jitter, Cycle to cycle

tjcyc-cyc

1 Measured into fixed 2 pF load cap. Input to output skew is measured at the first output edge following the corresponding input.

2 Measured from differential cross-point to differential cross-point.

3 All Bypass Mode Input-to-Output specs refer to the timing between an input edge and the specific output edge created by it.

4 This parameter is deterministic for a given device

5 Measured with scope averaging on to find mean value.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9EX21801AKLF | PLL BASED CLOCK DRIVER, PQCC72 |

| 9EX21801AKLFT | PLL BASED CLOCK DRIVER, PQCC72 |

| 9EX21831AKLFT | 21831 SERIES, PLL BASED CLOCK DRIVER, 18 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC72 |

| 9EX21831AKLF | 21831 SERIES, PLL BASED CLOCK DRIVER, 18 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC72 |

| 9FG104DGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9EX21501AKILFT | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 64-Pin VFQFPN EP T/R 制造商:Integrated Device Technology Inc 功能描述:64 MLF (LEAD FREE) - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:PCIE BUFFER - GEN2. 15 OUTPUTS w/2:1 INP |

| 9EX21501AKLF | 功能描述:時(shí)鐘緩沖器 PCIE BUFFER - GEN2. 15 OUTPUTS w/2:1 INP RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9EX21501AKLFT | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 PCIE BUFFER - GEN2. 15 OUTPUTS w/2:1 INP RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 9EX21531AKLF | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 PCIE BUFFER - GEN3, 15 OUTPUTS w/2:1 INP RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 9EX21531AKLFT | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Generator Single 64-Pin MLF T/R 制造商:Integrated Device Technology Inc 功能描述:64 MLF (LEAD FREE) - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:PCIE BUFFER - GEN3, 15 OUTPUTS w/2:1 INP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。