- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25565 > 9DB803DFLF (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF資料下載

參數(shù)資料

| 型號(hào): | 9DB803DFLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | 時(shí)鐘及定時(shí) |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封裝: | ROHS COMPLIANT, MO-118, SSOP-48 |

| 文件頁(yè)數(shù): | 2/21頁(yè) |

| 文件大小: | 174K |

| 代理商: | 9DB803DFLF |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

IDTTM/ICSTM

Eight Output Differential Buffer for PCIe Gen 2

ICS9DB803D

REV K 05/09/11

ICS9DB803D

Eight Output Differential Buffer for PCIe for Gen 2

10

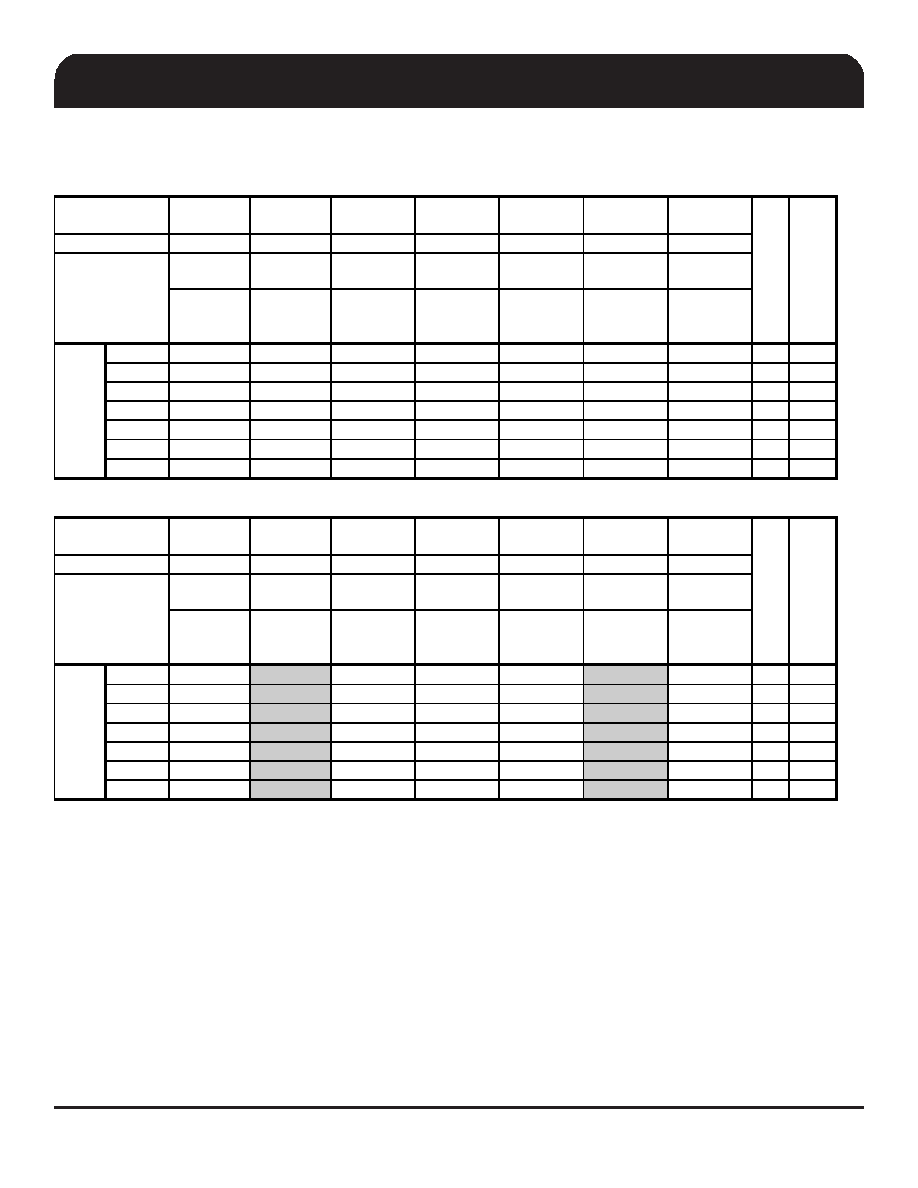

Clock Periods Differential Outputs with Spread Spectrum Enabled

1 Clock

1us

0.1s

1us

1 Clock

Lg-

-SSC

-ppm error

0ppm

+ ppm error

+SSC

Lg+

Absolute

Period

Short-term

Average

Long-Term

Average

Period

Long-Term

Average

Short-term

Average

Period

Minimum

Absolute

Period

Minimum

Absolute

Period

Minimum

Absolute

Period

Nominal

Maximum

DIF 100

9.87400

9.99900

10.00000

10.00100

10.05130

10.17630

ns

1,2,3

DIF 133

7.41425

7.49925

7.50000

7.50075

7.53845

7.62345

ns

1,2,4

DIF 166

5.91440

5.99940

6.00000

6.00060

6.03076

6.11576

ns

1,2,4

DIF 200

4.91450

4.99950

5.00000

5.00050

5.02563

5.11063

ns

1,2,4

DIF 266

3.66463

3.74963

3.75000

3.75038

3.76922

3.85422

ns

1,2,4

DIF 333

2.91470

2.99970

3.00000

3.00030

3.01538

3.10038

ns

1,2,4

DIF 400

2.41475

2.49975

2.50000

2.50025

2.51282

2.59782

ns

1,2,4

Clock Periods Differential Outputs with Spread Spectrum Disabled

1 Clock

1us

0.1s

1us

1 Clock

Lg-

-SSC

-ppm error

0ppm

+ ppm error

+SSC

Lg+

Absolute

Period

Short-term

Average

Long-Term

Average

Period

Long-Term

Average

Short-term

Average

Period

Minimum

Absolute

Period

Minimum

Absolute

Period

Minimum

Absolute

Period

Nominal

Maximum

DIF 100

9.87400

9.99900

10.00000

10.00100

10.17630

ns

1,2,3

DIF 133

7.41425

7.49925

7.50000

7.50075

7.62345

ns

1,2,4

DIF 166

5.91440

5.99940

6.00000

6.00060

6.11576

ns

1,2,4

DIF 200

4.91450

4.99950

5.00000

5.00050

5.11063

ns

1,2,4

DIF 266

3.66463

3.74963

3.75000

3.75038

3.85422

ns

1,2,4

DIF 333

2.91470

2.99970

3.00000

3.00030

3.10038

ns

1,2,4

DIF 400

2.41475

2.49975

2.50000

2.50025

2.59782

ns

1,2,4

1Guaranteed by design and characterization, not 100% tested in production.

3 Driven by SRC output of main clock, PLL or Bypass mode

4 Driven by CPU output of CK410/CK505 main clock, Bypass mode only

Definition

Units

Si

g

n

a

lN

a

m

e

S

igna

lN

a

m

e

Measurement

Window

Symbol

2 All Long Term Accuracy specifications are guaranteed with the assumption that the input clock complies with

CK409/CK410/CK505 accuracy requirements. The 9DB403/803 itself does not contribute to ppm error.

Notes

Definition

Measurement

Window

Units

Symbol

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9DB803DFILF | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB803DGLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB803DFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB803DGT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB823BFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9DB803DFLFT | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB803DGILF | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB803DGILFT | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB803DGLF | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB803DGLFT | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。