- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25564 > 9DB202CFLF (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | 9DB202CFLF |

| 廠(chǎng)商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | 時(shí)鐘及定時(shí) |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 封裝: | 5.30 X 7.20 MM, 1.75 MM HEIGHT, ROHS COMPLIANT, MO-150, SSOP-20 |

| 文件頁(yè)數(shù): | 1/13頁(yè) |

| 文件大小: | 673K |

| 代理商: | 9DB202CFLF |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)

PCI EXPRESS JITTER ATTENUATOR

ICS9DB202

IDT / ICS PCI EXPRESS JITTER ATTENUATOR

1

ICS9DB202CG REV B JULY 14, 2006

GENERAL DESCRIPTION

The ICS9DB202 is a high perfromance 1-to-2

Differential-to-HCSL Jitter Attenuator designed for

use in PCI Express systems. In some PCI

Express systems, such as those found in desktop

PCs, the PCI Express clocks are generated from

a low bandwidth, high phase noise PLL frequency synthesizer.

In these systems, a jitter-attenuating device may be necessary

in order to reduce high frequency random and deterministic

jitter components from the PLL synthesizer and from the system

board. The ICS9DB202 has two PLL bandwidth modes. In low

bandwidth mode, the PLL loop bandwidth is 500kHz. This setting

offers the best jitter attenuation and is still high enough to pass

a triangular input spread spectrum profile. In high bandwidth

mode, the PLL bandwidth is at 1MHz and allows the PLL to

pass more spread spectrum modulation.

For serdes which have x10 reference multipliers instead of x12.5

multipliers, each of the two PCI Express outputs (PCIEX0:1)

can be set for 125MHz instead of 100MHz by configuring the

appropriate frequency select pins (FS0:1).

FEATURES

Two 0.7V current mode differential HCSL output pairs

One differential clock input

CLK and nCLK supports the following input types:

LVPECL, LVDS, LVHSTL, SSTL, HCSL

Maximum output frequency: 140MHz

Input frequency range: 90MHz - 140MHz

VCO range: 450MHz - 700MHz

Output skew: 110ps (maximum)

Cycle-to-cycle jitter: 110ps (maximum)

RMS phase jitter @ 100MHz, (1.5MHz - 22MHz):

2.42ps (typical)

3.3V operating supply

0°C to 70°C ambient operating temperature

Available in both standard and lead-free RoHS compliant

packages

Industrial temperature information available upon request

HiPerClockS

ICS

PIN ASSIGNMENT

nOE0

nCLK

CLK

BYPASS

nOE1

PCIEXT0

nPCIEXC0

PCIEXT1

nPCIEXC1

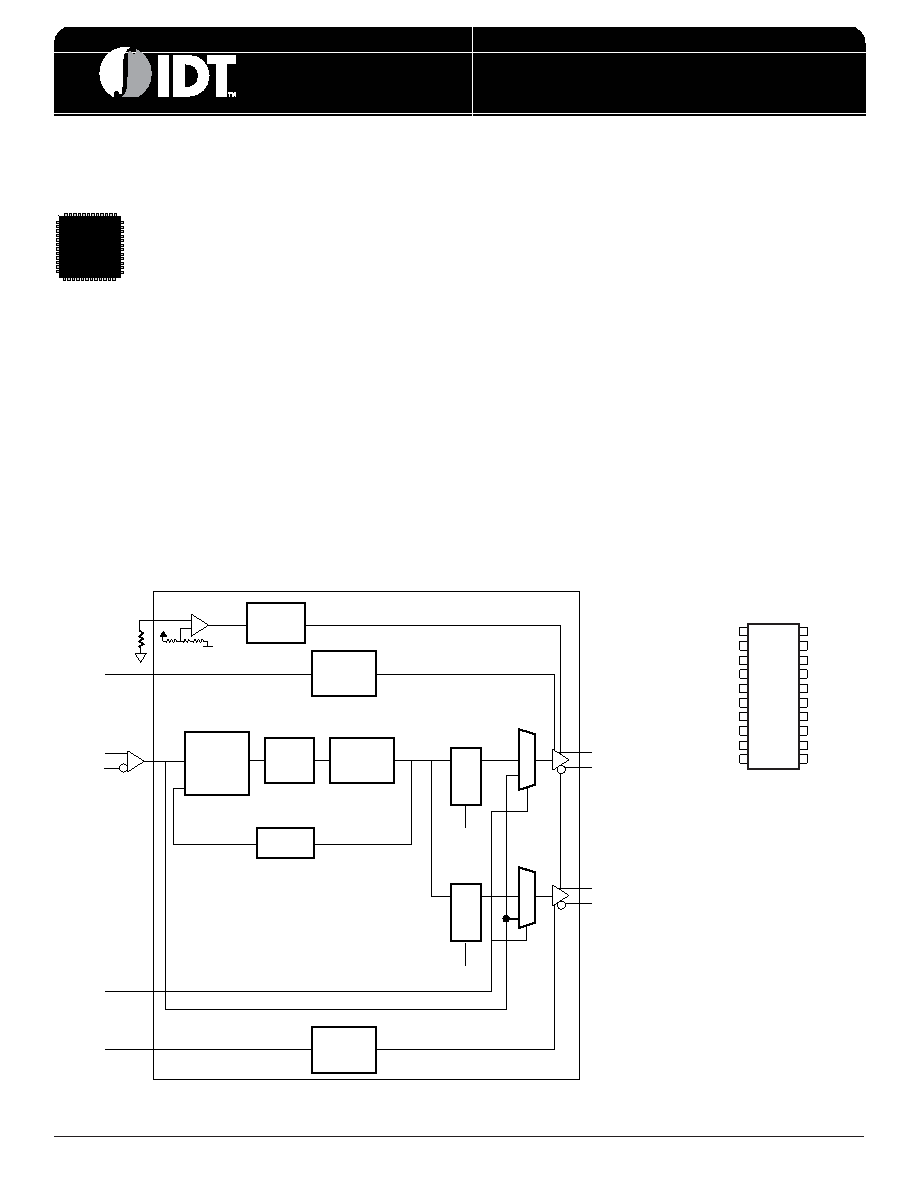

BLOCK DIAGRAM

ICS9DB202

20-Lead TSSOP

6.50mm x 4.40mm x 0.92

package body

G Package

Top View

ICS9DB202

20-Lead, 209-MIL SSOP

5.30mm x 7.20mm x 1.75mm

body package

F Package

Top View

Phase

Detector

VCO

Loop

Filter

1 HiZ

0 Enabled

1 HiZ

0 Enabled

0 ÷4

1 ÷5

0 ÷5

1 ÷4

FS0

FS1

Internal Feedback

÷5

Current

Set

-

+

0

1

0

1

IREF

PLL_BW

CLK

nCLK

FS0

VDD

GND

PCIEXT0

PCIEXC0

VDD

nOE0

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

VDDA

BYPASS

IREF

FS1

VDD

GND

PCIEXT1

PCIEXC1

VDD

nOE1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9DB202CFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 9DB202CK-01T | 9DB SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC32 |

| 9DB206CFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB206CF | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB206CLT | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9DB202CFLFT | 功能描述:時(shí)鐘緩沖器 2 HCSL Output PCIe Buffer RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB202CFT | 制造商:Integrated Device Technology Inc 功能描述:9DB202CFT - Tape and Reel |

| 9DB202CG | 制造商:Integrated Device Technology Inc 功能描述:9DB202CG - Rail/Tube |

| 9DB202CGLF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 2 HCSL Output PCIe Buffer RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9DB202CGLFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 2 HCSL Output PCIe Buffer RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。