- 您現(xiàn)在的位置:買賣IC網 > PDF目錄25564 > 9DB1933AKLFT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 19 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC72 PDF資料下載

參數(shù)資料

| 型號: | 9DB1933AKLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 19 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC72 |

| 封裝: | ROHS COMPLIANT, PLASTIC, QFN-72 |

| 文件頁數(shù): | 12/17頁 |

| 文件大小: | 174K |

| 代理商: | 9DB1933AKLFT |

IDT

Nineteen Output Differential Buffer for PCIe Gen3

9DB1933

Nineteen Output Differential Buffer for PCIe Gen3

4

1676A—07/12/10

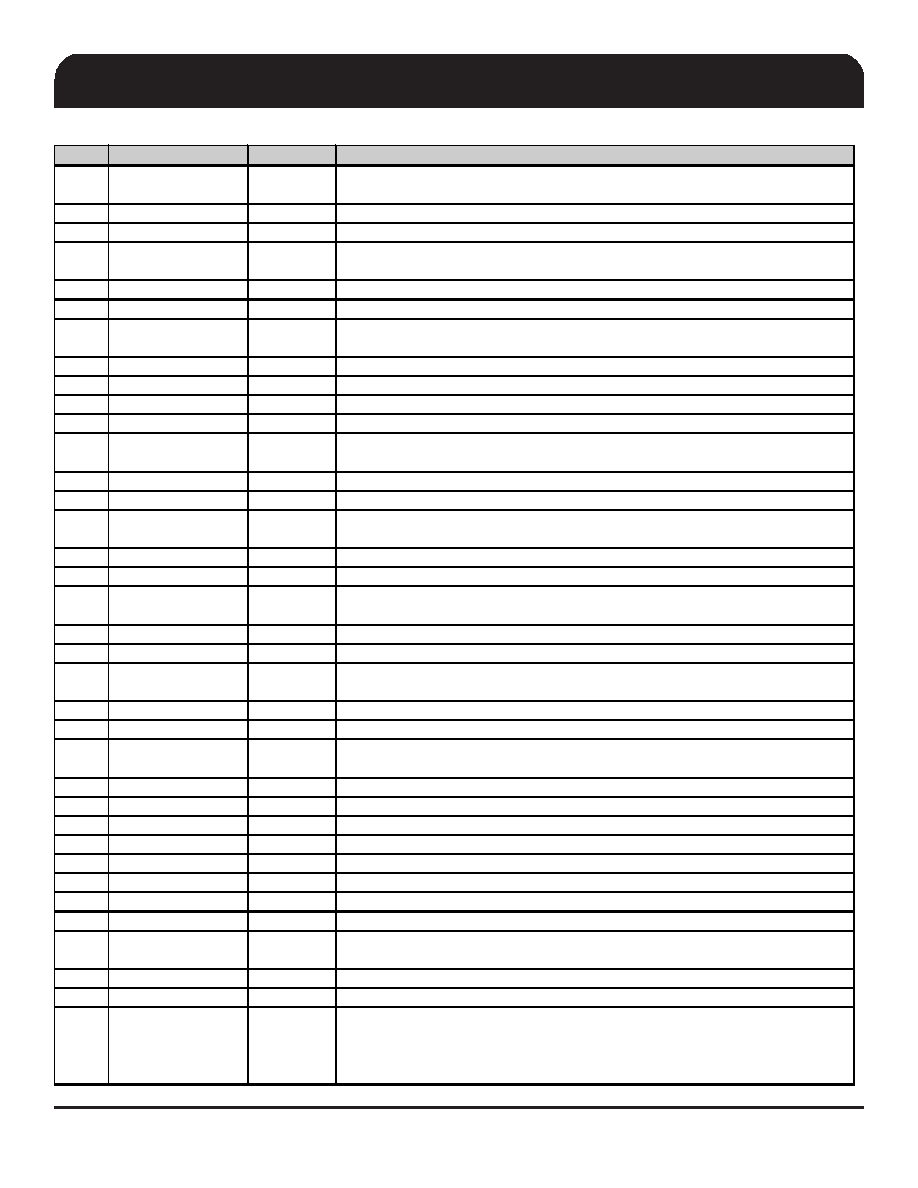

Pin Description (cont.)

PIN #

PIN NAME

PIN TYPE

DESCRIPTION

37

OE9#

IN

Active low input for enabling DIF pair 9.

1 =disable outputs, 0 = enable outputs

38

DIF_9

OUT

0.7V differential true clock output

39

DIF_9#

OUT

0.7V differential Complementary clock output

40

OE10#

IN

Active low input for enabling DIF pair 10.

1 =disable outputs, 0 = enable outputs

41

DIF_10

OUT

0.7V differential true clock output

42

DIF_10#

OUT

0.7V differential Complementary clock output

43

OE11#

IN

Active low input for enabling DIF pair 11.

1 =disable outputs, 0 = enable outputs

44

DIF_11

OUT

0.7V differential true clock output

45

DIF_11#

OUT

0.7V differential Complementary clock output

46

GND

PWR

Ground pin.

47

VDD

PWR

Power supply, nominal 3.3V

48

OE12#

IN

Active low input for enabling DIF pair 12.

1 =disable outputs, 0 = enable outputs

49

DIF_12

OUT

0.7V differential true clock output

50

DIF_12#

OUT

0.7V differential Complementary clock output

51

OE13#

IN

Active low input for enabling DIF pair 13.

1 =disable outputs, 0 = enable outputs

52

DIF_13

OUT

0.7V differential true clock output

53

DIF_13#

OUT

0.7V differential Complementary clock output

54

OE14#

IN

Active low input for enabling DIF pair 14.

1 =disable outputs, 0 = enable outputs

55

DIF_14

OUT

0.7V differential true clock output

56

DIF_14#

OUT

0.7V differential Complementary clock output

57

CKPWRGD/PD#

IN

A rising edge samples latched inputs and release Power Down Mode, a low

puts the part into power down mode and tristates all outputs.

58

DIF_15

OUT

0.7V differential true clock output

59

DIF_15#

OUT

0.7V differential Complementary clock output

60

OE_15_16#

IN

Active low input for enabling DIF pair 15 and 16.

1 = tri-state outputs, 0 = enable outputs

61

DIF_ 16

OUT

0.7V differential true clock output

62

DIF_16#

OUT

0.7V differential Complementary clock output

63

VDD

PWR

Power supply, nominal 3.3V

64

GND

PWR

Ground pin.

65

DIF_17

OUT

0.7V differential true clock output

66

DIF_17#

OUT

0.7V differential Complementary clock output

67

DIF_18

OUT

0.7V differential true clock output

68

DIF_18#

OUT

0.7V differential Complementary clock output

69

OE_17_18#

IN

Active low input for enabling DIF pair 17, 18.

1 = tri-state outputs, 0 = enable outputs

70

DIF_IN

IN

0.7 V Differential TRUE input

71

DIF_IN#

IN

0.7 V Differential Complementary Input

72

SMB_A2_PLLBYP#

IN

SMBus address bit 2. When Low, the part operates as a fanout buffer with the

PLL bypassed. When High, the part operates as a zero-delay buffer (ZDB) with

the PLL operating.

0 = fanout mode (PLL bypassed), 1 = ZDB mode (PLL used)

相關PDF資料 |

PDF描述 |

|---|---|

| 9DB202CGLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 9DB202CFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 9DB202CFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 9DB202CK-01T | 9DB SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC32 |

| 9DB206CFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 9DB202CF | 制造商:Integrated Device Technology Inc 功能描述:9DB202CF - Rail/Tube |

| 9DB202CFLF | 功能描述:時鐘合成器/抖動清除器 2 HCSL Output PCIe Buffer RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9DB202CFLFT | 功能描述:時鐘緩沖器 2 HCSL Output PCIe Buffer RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB202CFT | 制造商:Integrated Device Technology Inc 功能描述:9DB202CFT - Tape and Reel |

| 9DB202CG | 制造商:Integrated Device Technology Inc 功能描述:9DB202CG - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。