- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄24830 > 935269256557 (NXP SEMICONDUCTORS) 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | 935269256557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 |

| 封裝: | 12 X 12 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-315-1, LQFP-80 |

| 文件頁(yè)數(shù): | 8/36頁(yè) |

| 文件大小: | 145K |

| 代理商: | 935269256557 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

2000 Nov 17

16

Philips Semiconductors

Preliminary specication

1394 SBP-2 link layer controller

SAA7356HL

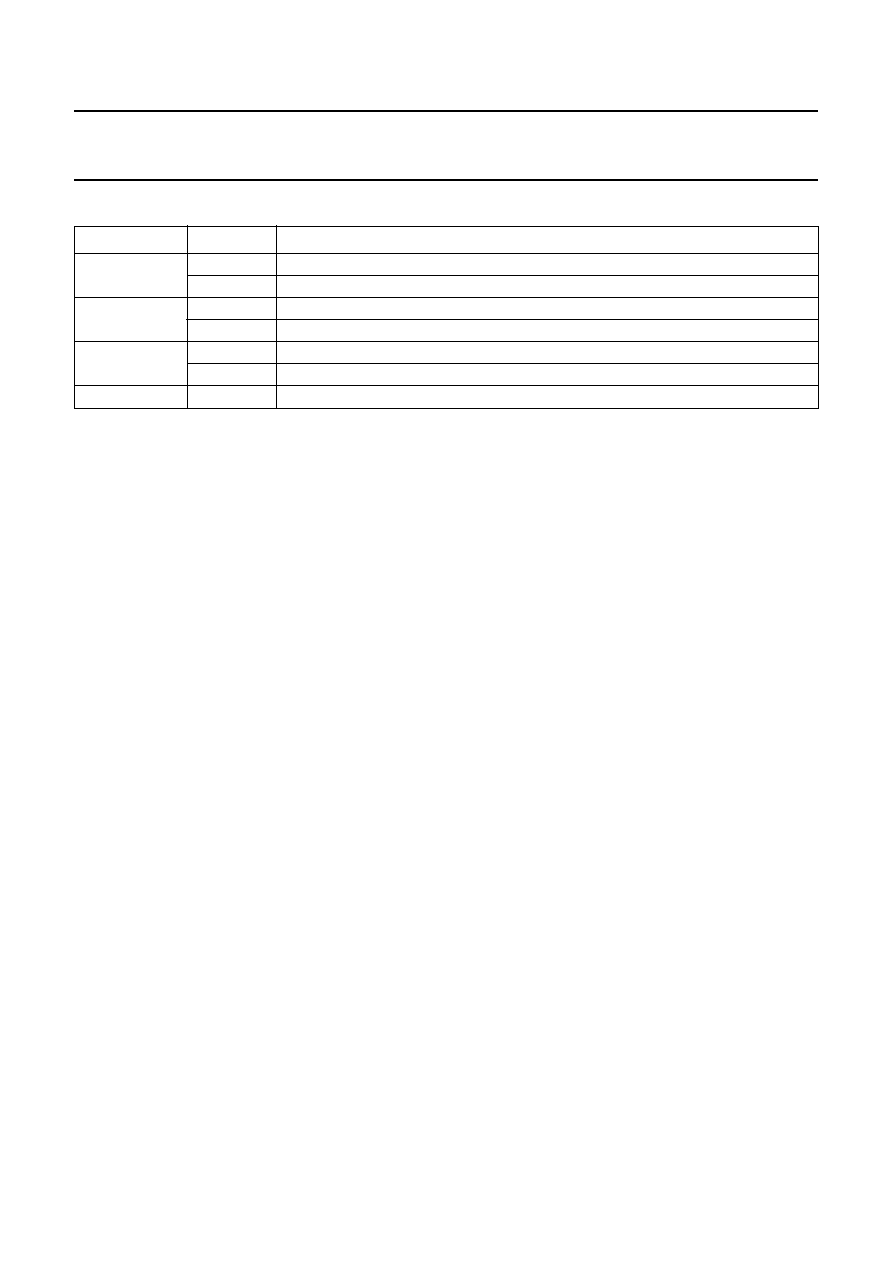

Table 8

Denition of the InterruptReason, InterruptEnable and InterruptSet register elds

MNEMONIC

VALUE

COMMENT

CmdClr

0

default condition: no action occurred

1

the SAA7356HL device has acknowledged the write to the CmdFromMicro register

BusReset

0

default condition: no action occurred

1

the SAA7356HL has detected a serial bus reset

CmdMicro

0

default condition: no action occurred

1

the SAA7356HL has written a command into the CmdToMicro register

Reserved

X

reserved and set to zero

8.4

RAM access for parameter passing

Within the SAA7356HL there is a 16 kbyte RAM. This is

shared between: the IEEE1394 transaction FIFOs,

the code for the automation engine and its local storage

requirements, and the shared memory area for

communications with the microcontroller.

The SAA7356HL user must understand how this shared

memory is accessed in order to write and read the

communications parameters. Each of the read and write

accesses to the FIFOs are byte-wide and the offset

addresses are byte offsets.

8.4.1

REGISTER ACCESS

The RAM can be directly accessed to upload the code into

the SAA7356HL. The C-structure for the registers for the

RAM access is shown below.

struct RAM {

U16; offset; // absolute offset into the RAM

U8; next; // read/write data at offset and

post-increment

U8; current; // read/write data at offset

};

The RAM.Offset field allows the microcontroller to access

anywhere within the SAA7356HL RAM. The RAM.Next

accesses will access the RAM.Offset address and

post-increment the offset pointer.

Accesses to the RAM.Current address allow reads and

writes to the data in the RAM.Offset location without

altering the RAM.Offset address.

The ability to write to anywhere within the RAM is used for

the power-on sequence.

8.4.2

REGISTER DEFINITIONS FOR THE REGISTER ACCESS

METHOD

This section defines the register structure for the RAM

registers.

The RAM.Offset registers are used to index into the RAM

inside the SAA7356HL. The index is a byte address. The

RAM.Offset register definition is shown in Table 9.

The RAM.Next register is used to read or write to the RAM

location addressed by the RAM.Offset register. Once an

access has been made, the value of the RAM.Offset

register is incremented to simplify the process of reading

or writing contiguous memory areas. The RAM.Next

register definition is shown in Table 10.

The RAM.Current register is used to read or write to the

RAM location addressed by the RAM.Offset register.

Once an access has been made there is no change to the

RAM.Offset register. The RAM.Current register definition

is shown in Table 11.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935264570557 | 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 |

| 0803-7700-02 | Integrated VDSL Filter/Hybrid Solution |

| 935269451118 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 935269451112 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 0803-7700-03 | VDSL / PSTN CO Splitter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

| 935270792551 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。