- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24830 > 935269132118 (NXP SEMICONDUCTORS) PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF資料下載

參數(shù)資料

| 型號: | 935269132118 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 時鐘及定時 |

| 英文描述: | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封裝: | 6.10 MM, PLASTIC, MO-153, SOT-362-1, TSSOP-48 |

| 文件頁數(shù): | 11/15頁 |

| 文件大小: | 113K |

| 代理商: | 935269132118 |

Philips Semiconductors

Product data

PCKV857

70–190 MHz differential 1:10 clock driver

2002 Sep 13

5

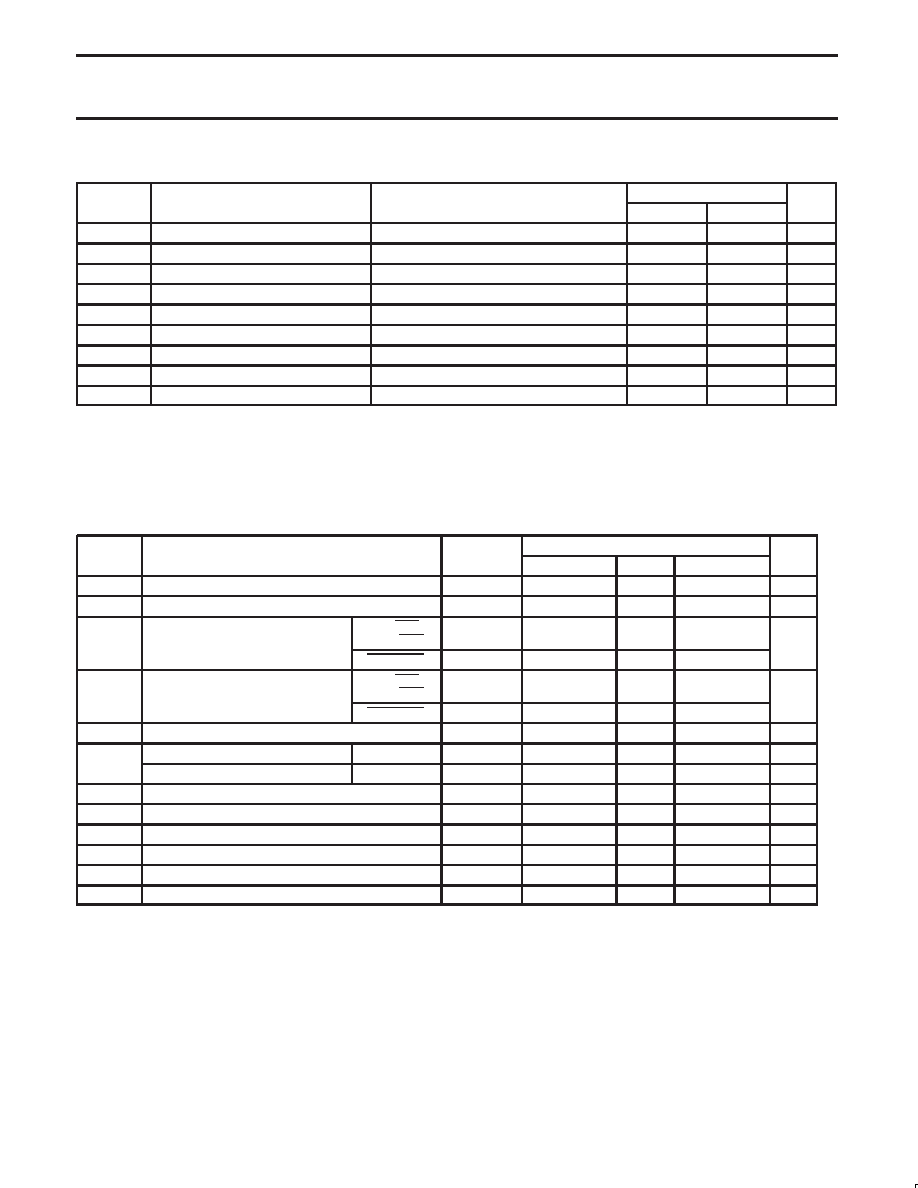

ABSOLUTE MAXIMUM RATINGS1

SYMBOL

PARAMETER

CONDITION

LIMITS

UNIT

SYMBOL

PARAMETER

CONDITION

MIN

MAX

UNIT

VDDQ

Supply voltage range

0.5

3.6

V

AVDD

Supply voltage range

0.5

3.6

V

VI

Input voltage range

see Notes 2 and 3

–0.5

VDDQ + 0.5

V

VO

Output voltage range

see Notes 2 and 3

–0.5

VDDQ + 0.5

V

IIK

Input clamp current

VI < 0 or VI >VDDQ

—

±50

mA

IOK

Output clamp current

VO < 0 or VO >VDDQ

—

±50

mA

IO

Continuous output current

VO = 0 to VDDQ

—

±50

mA

Continuous current to GND or VDDQ

—

±100

mA

Tstg

Storage temperature range

–65

+150

°C

NOTES:

1. Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating

conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

3. This value is limited to 3.6 V maximum.

RECOMMENDED OPERATING CONDITIONS1

SYMBOL

PARAMETER

CONDITION

LIMITS

UNIT

SYMBOL

PARAMETER

CONDITION

MIN

TYP

MAX

UNIT

VDDQ

Supply voltage range

2.3

—

2.7

V

AVDD

Supply voltage range

2.2

—

2.7

V

VIL

Low level input voltage

CLK, CLK,

FBIN, FBIN

—

VDDQ/2 0.18

V

IL

g

PWRDWN

0.3

—

0.7

VIH

High level input voltage

CLK, CLK,

FBIN, FBIN

VDDQ/2 + 0.18

—

V

IH

gg

PWRDWN

1.7

—

VDDQ + 0.3

DC input signal voltage

Note 2

0.3

—

VDDQ

V

DC differential input signal voltage

CLK, FBIN

Note 3

0.36

—

VDDQ + 0.6

V

VID

AC differential input signal voltage

CLK, FBIN

Note 3

0.7

—

VDDQ + 0.6

V

VOX

Output differential cross-voltage

Note 4

VDDQ/2 0.2

VDDQ/2

VDDQ/2 + 0.2

V

VIX

Input differential cross-voltage

Note 4

VDDQ/2 0.2

—

VDDQ/2 + 0.2

V

IOH

High-level output current

—

12

mA

IOL

Low-level output current

—

12

mA

SR

Input slew rate

1

—

4

V/ns

Tamb

Operating free-air temperature

0

—

70

°C

NOTES:

1. Unused inputs must be held high or low to prevent them from floating.

2. DC input signal voltage specifies the allowable DC execution of differential input.

3. Differential input signal voltage specifies the differential voltage |VTR – VCP| required for switching, where VTR is the true input level and

VCP is the complementary input level.

4. Differential cross-point voltage is expected to track variations of VCC and is the voltage at which the differential signals must be crossing.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935269202112 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935269193112 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935269192112 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935269192118 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935269202118 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

| 935270792551 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。