- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36339 > 935267395518 (NXP SEMICONDUCTORS) COLOR SIGNAL DECODER, PBGA156 PDF資料下載

參數(shù)資料

| 型號(hào): | 935267395518 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL DECODER, PBGA156 |

| 封裝: | 15 X 15 MM, 1.15 MM HEIGHT, PLASTIC, MS-034, SOT-472-1, BGA-156 |

| 文件頁數(shù): | 56/178頁 |

| 文件大小: | 988K |

| 代理商: | 935267395518 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當(dāng)前第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁

2004 Jul 22

149

Philips Semiconductors

Product specication

Multistandard video decoder with adaptive

comb lter and component video input

SAA7118

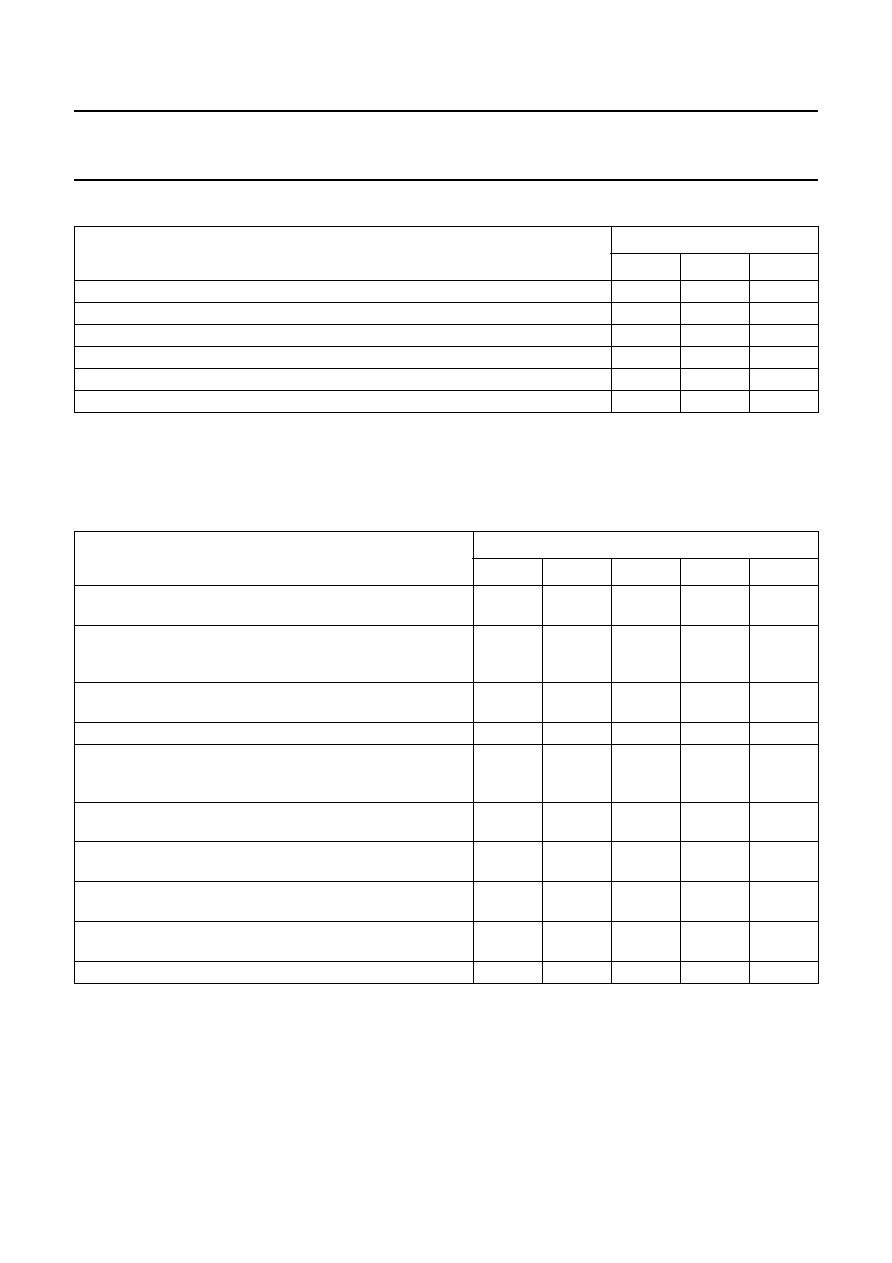

Table 111 Task handling control; register set A [90H[2:0]] and B [C0H[2:0]]; note 1

Note

1. X = don’t care.

15.7.6

SUBADDRESSES 91H TO 93H

Table 112 X port formats and conguration; register set A [91H[7:3]] and B [C1H[7:3]]; note 1

Note

1. X = don’t care.

EVENT HANDLER CONTROL

CONTROL BITS D2 TO D0

RPTSK

STRC1

STRC0

Event handler triggers immediately after nishing a task

X

0

Event handler triggers with next V-sync

X

0

1

Event handler triggers with eld ID = 0

X

1

0

Event handler triggers with eld ID = 1

X

1

If active task is nished, handling is taken over by the next task

0

X

Active task is repeated once, before handling is taken over by the next task

1

X

SCALER INPUT FORMAT AND CONFIGURATION SOURCE

SELECTION

CONTROL BITS D7 TO D3

CONLV

HLDFV

SCSRC1 SCSRC0

SCRQE

Only if XRQT[83H[2]] = 1: scaler input source reacts on

SAA7118 request

XXXX

0

Scaler input source is a continuous data stream, which cannot

be interrupted (must be logic 1, if SAA7118 decoder part is

source of scaler or XRQT[83H[2]] = 0)

XXXX

1

Scaler input source is data from decoder, data type is

provided according to Table 15

XX

0

X

Scaler input source is Y-CB-CR data from X port

X

0

1

X

Scaler input source is raw digital CVBS from selected analog

channel, for backward compatibility only, further use is not

recommended

XX

1

0

X

Scaler input source is raw digital CVBS (or 16-bit Y + CB-CR,if

no 16-bit outputs are active) from X port

XX

1

X

SAV/EAV code bits D6 and D5 (F and V) may change

between SAV and EAV

X

0

XXX

SAV/EAV code bits D6 and D5 (F and V) are synchronized to

scalers output line start

X

1

XXX

SAV/EAV code bit D5 (V) and V gate on pin IGPV as

generated by the internal processing; see Fig.43

0

XXXX

SAV/EAV code bit D5 (V) and V gate are inverted

1

XXXX

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935267395551 | COLOR SIGNAL DECODER, PBGA156 |

| 935267395557 | COLOR SIGNAL DECODER, PBGA156 |

| 935268832557 | COLOR SIGNAL DECODER, PQFP160 |

| 935273916518 | COLOR SIGNAL DECODER, PBGA156 |

| 935273916557 | COLOR SIGNAL DECODER, PBGA156 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。