- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24811 > 935263687551 (NXP SEMICONDUCTORS) 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PBGA64 PDF資料下載

參數(shù)資料

| 型號: | 935263687551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PBGA64 |

| 封裝: | PLASTIC, LFBGA-64 |

| 文件頁數(shù): | 3/22頁 |

| 文件大?。?/td> | 170K |

| 代理商: | 935263687551 |

Philips Semiconductors

Preliminary specification

PDI1394P11A

3-port physical layer interface

1999 Mar 10

11

17.1

Arbitrated (short) Bus Reset

A 1394-1995 software initiated bus reset assumes that the state of

the bus is unknown when reset occurs and requires that the reset be

long enough to permit the longest transaction to finish and still

complete reset (167

s min. to 250s max.). The total duration of bus

initialization is longer than the nominal isochronous cycle time

(125

s) and may disrupt two isochronous periods. This compels

device designers to add additional buffer depth to preserve the

smooth flow of isochronous data from the perspective of their

application. If a node that initiates a reset arbitrates for control of the

bus prior to asserting reset, arbitration time can be shortened

significantly (1.3

s min. to 80s max.). This 1394a concept is known

as Arbitrated (short) Bus Reset, and is incorporated in the

PDI1394P11A.

The TESTM2 (pin 21) pins is used to enable Arbitrated (short) Bus

Reset mode. In 1394-1995 mode, this pin is tied high. In this mode,

an arbitrated bus reset cannot be initiated from this node and will be

treated as a “l(fā)ong” bus reset if initiated by another node. In

accordance with the 1394-1995 spec, all bus resets on the entire

bus will be “l(fā)ong”.

To enable Arbitrated (short) Bus Reset mode, set TESTM2 low.

With the part in this mode, writing a 1 to the ISBR (Initiate Short Bus

Reset) bit (bit 7) of Phy register 9 initiates an arbitrated bus reset.

This mode also allows the Phy to recognize arbitrated bus resets

initiated by other nodes. Non-arbitrated bus resets can still be

initiated from this node and are recognized and processed correctly

when initiated by another node.

17.2

Setting the CPS Trip Point

The Cable Power Status (CPS) pin (pin 23) is used to monitor the

cable power. When cable power voltage has dropped too low for

reliable operation, internal circuitry trips, which clears the CPS bits

in the Phy registers (bit 7 of register 0, and bit 2 of register 6). This

action causes a cable power status interrupt which sets the CPSint

bit in the Phy registers (bit 1 of register 6). This bit can be cleared by

a hardware reset or by writing a 0 to the CPSint bit. However, if the

CPS input is still low, another cable-power status interrupt

immediately occurs. The cable voltage at which these events occur

is adjustable on the PDI1394P11A.

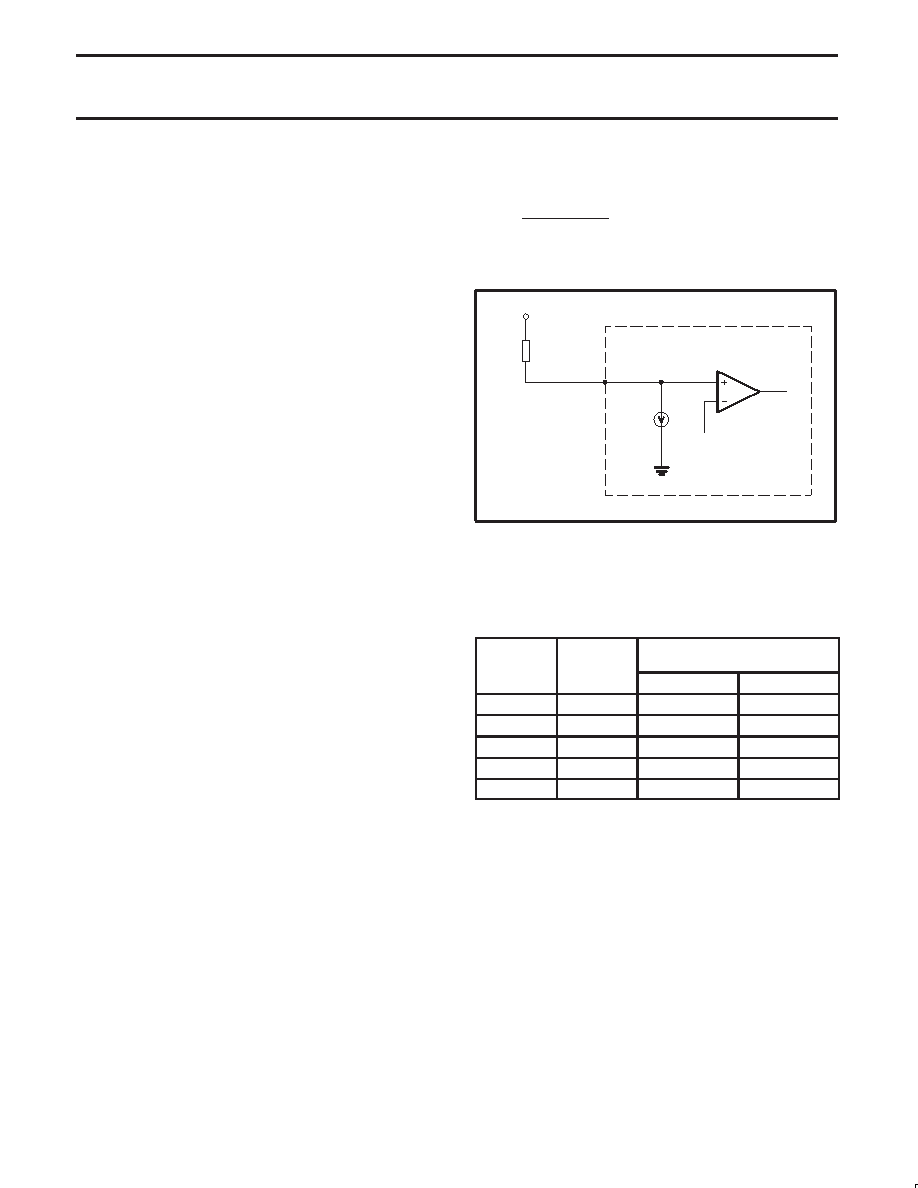

The external resistor (R) needed to set the CPS trip voltage (Vcable)

to a desired voltage can be calculated using the following equation:

R

+

(V

cable * 1.85V)

10

mA

The external and internal circuitry associated with the CPS pin is

illustrated in Figure 5.

COMPARATOR

Vcomp

1.85V

Vcable

R

Phy

CPS

Icomp

10

A

SV00921

Figure 5.

Some typical threshold voltage values and their associated resistor

values are shown in Table 1.

Table 1. Typical threshold voltage values

Vcable (V)

R (k

)

Vcable DETECTOR

TOLERANCE % WITH:

cable ()

(

)

R of 5%

R of 2%

5

315

6.8

4.4

6

415

7.3

4.8

7

515

7.8

5.2

8

615

8.3

5.6

9

715

8.8

6.0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 08-03-0303 | Crimp Socket Contact; Wire Size (AWG):24-18; Contact Material:Brass RoHS Compliant: Yes |

| 08-03-0304 | CONNECTOR CONTACT,SKT,CRIMP TERMINAL |

| 08-05-0301 | Crimp Socket Contact; Wire Size (AWG):24-18; Contact Material:Brass RoHS Compliant: Yes |

| 08-05-0302 | Crimp Socket Contact; Wire Size (AWG):24-18; Contact Material:Brass RoHS Compliant: Yes |

| 08-05-0305 | BRASS, GOLD FINISH, WIRE TERMINAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。