- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24693 > 934054560127 (NXP SEMICONDUCTORS) 19 A, 55 V, 0.075 ohm, N-CHANNEL, Si, POWER, MOSFET, TO220-AB PDF資料下載

參數(shù)資料

| 型號: | 934054560127 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | JFETs |

| 英文描述: | 19 A, 55 V, 0.075 ohm, N-CHANNEL, Si, POWER, MOSFET, TO220-AB |

| 封裝: | TO-220AB, 3 PIN |

| 文件頁數(shù): | 6/13頁 |

| 文件大小: | 147K |

| 代理商: | 934054560127 |

Philips Semiconductors

Product specification

N-channel TrenchMOS

transistor

PHP21N06LT, PHB21N06LT

Logic level FET

PHD21N06LT

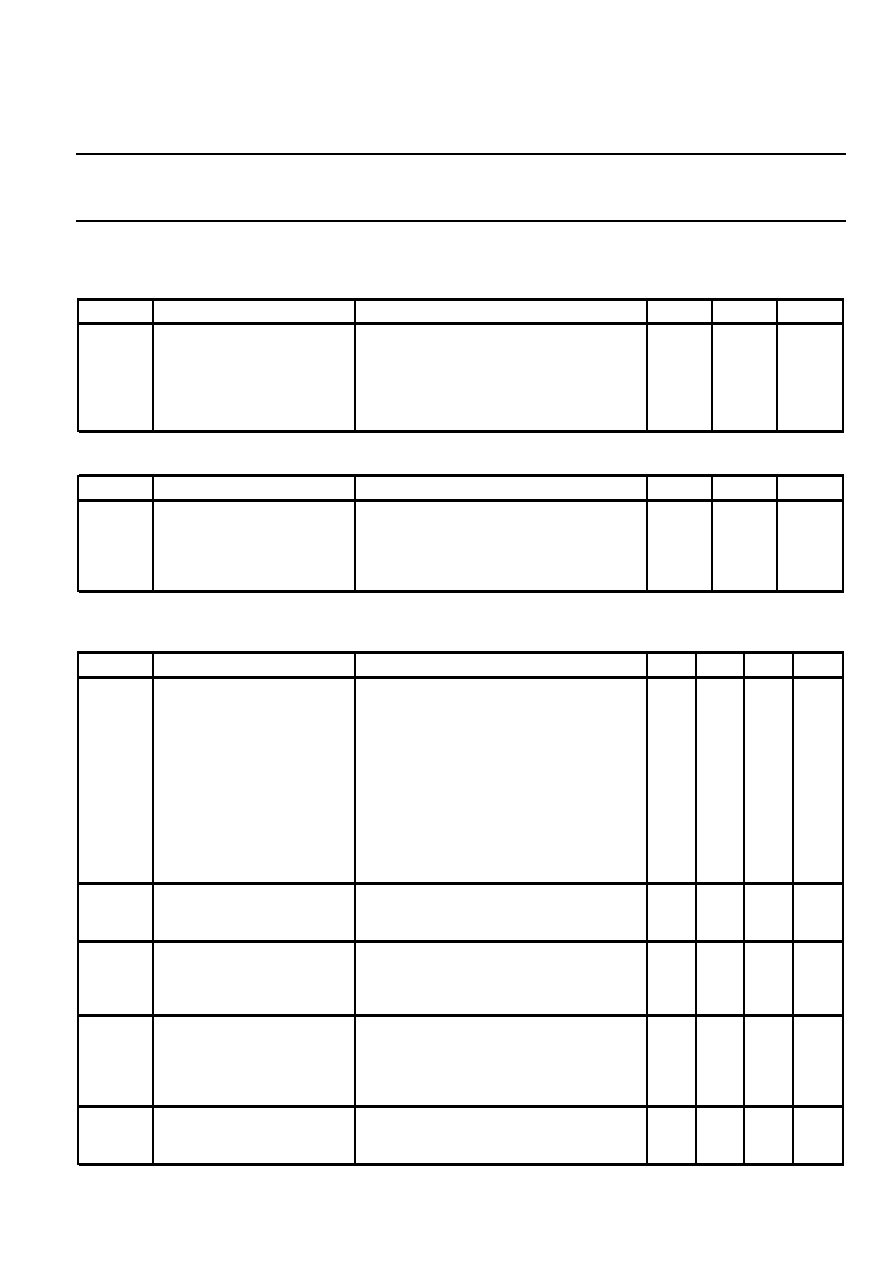

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

E

AS

Non-repetitive avalanche

Unclamped inductive load, I

AS = 9.7 A;

-

34

mJ

energy

t

p = 100 s; Tj prior to avalanche = 25C;

V

DD ≤ 25 V; RGS = 50 ; VGS = 5 V; refer to

fig:15

I

AS

Peak non-repetitive

-

19

A

avalanche current

THERMAL RESISTANCES

SYMBOL PARAMETER

CONDITIONS

TYP.

MAX.

UNIT

R

th j-mb

Thermal resistance junction

-

2.7

K/W

to mounting base

R

th j-a

Thermal resistance junction

SOT78 package, in free air

60

-

K/W

to ambient

SOT428 and SOT404 package, pcb

50

-

K/W

mounted, minimum footprint

ELECTRICAL CHARACTERISTICS

T

j= 25C

unless otherwise specified

SYMBOL PARAMETER

CONDITIONS

MIN.

TYP. MAX. UNIT

V

(BR)DSS

Drain-source breakdown

V

GS = 0 V; ID = 0.25 mA;

55

-

V

voltage

T

j = -55C

50

-

V

GS(TO)

Gate threshold voltage

V

DS = VGS; ID = 1 mA

1.0

1.5

2.0

V

T

j = 175C

0.5

-

V

T

j = -55C

-

2.3

V

R

DS(ON)

Drain-source on-state

V

GS = 10 V; ID = 10 A

-

55

70

m

resistance

V

GS = 5 V; ID = 10 A

-

60

75

m

T

j = 175C

-

158

m

g

fs

Forward transconductance

V

DS = 25 V; ID = 10 A

5

13

-

S

I

GSS

Gate source leakage current V

GS = ±5 V; VDS = 0 V

-

10

100

nA

I

DSS

Zero gate voltage drain

V

DS = 55 V; VGS = 0 V;

-

0.05

10

A

current

T

j = 175C

-

500

A

Q

g(tot)

Total gate charge

I

D = 20 A; VDD = 44 V; VGS = 5 V

-

9.4

-

nC

Q

gs

Gate-source charge

-

2.2

-

nC

Q

gd

Gate-drain (Miller) charge

-

5.4

-

nC

t

d on

Turn-on delay time

V

DD = 30 V; RD = 1.2 ;-

7

15

ns

t

r

Turn-on rise time

R

G = 10 ; VGS = 5 V

-

88

120

ns

t

d off

Turn-off delay time

Resistive load

-

25

40

ns

t

f

Turn-off fall time

-

25

45

ns

L

d

Internal drain inductance

Measured from tab to centre of die

-

3.5

-

nH

L

d

Internal drain inductance

Measured from drain lead to centre of die

-

4.5

-

nH

(SOT78 package only)

L

s

Internal source inductance

Measured from source lead to source

-

7.5

-

nH

bond pad

C

iss

Input capacitance

V

GS = 0 V; VDS = 25 V; f = 1 MHz

-

466

650

pF

C

oss

Output capacitance

-

95

135

pF

C

rss

Feedback capacitance

-

71

85

pF

August 1999

2

Rev 1.500

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 934055349118 | 19 A, 55 V, 0.075 ohm, N-CHANNEL, Si, POWER, MOSFET |

| 05G4B48 | Silicon Diffused Type Rectifier Stack |

| 934054590135 | 4.9 A, 55 V, 0.04 ohm, N-CHANNEL, Si, POWER, MOSFET |

| 934054610135 | 3.5 A, 55 V, 0.08 ohm, N-CHANNEL, Si, POWER, MOSFET |

| 934054620135 | 5.5 A, 55 V, 0.15 ohm, N-CHANNEL, Si, POWER, MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 934054713215 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TXSTR |

| 934054900215 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TXSTR SGNL |

| 934054930215 | 制造商:NXP Semiconductors 功能描述:Diode Schottky 40V 0.2A 3-Pin TO-236AB T/R |

| 934054945115 | 制造商:NXP Semiconductors 功能描述:Diode Switching 100V 0.25A 2-Pin SOD-323 T/R |

| 934055092127 | 制造商:NXP Semiconductors 功能描述:H-OUT #7460 |

發(fā)布緊急采購,3分鐘左右您將得到回復。