- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378216 > 82572EI (INTEL CORP) Gigabit Ethernet Controller PDF資料下載

參數(shù)資料

| 型號: | 82572EI |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Gigabit Ethernet Controller |

| 中文描述: | 1 CHANNEL(S), 1000M bps, LOCAL AREA NETWORK CONTROLLER, BGA256 |

| 封裝: | 17 X 17 MM, FC-BGA-256 |

| 文件頁數(shù): | 11/58頁 |

| 文件大小: | 318K |

| 代理商: | 82572EI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

Product Datasheet

5

82571EB/82572EI Gigabit Ethernet Controller

2.0

Features of the 82571EB/82572EI Gigabit Ethernet

Controller

2.1

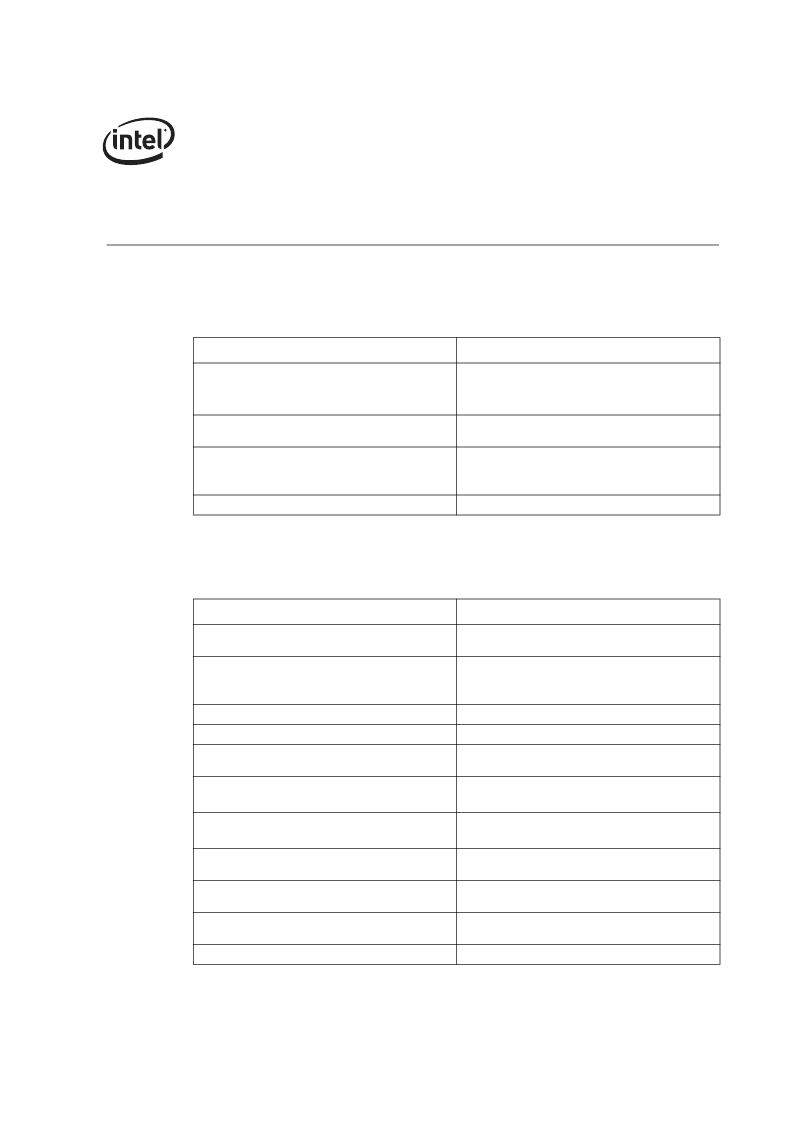

PCI Express Features

2.2

MAC-Specific Features

Features

Benefits

Uses x4 PCI Express interface on MCH device

Bus sharing not required

Low latency path to memory

Relieves congestion for IO devices

Peak bandwidth 2 GB/s in each direction per PCI Express

lane

Supports Gigabit Ethernet at full wire speed

PCI Express Power Management

Compatible extensions to PCI power management and

ACPI

PE_WAKE_n available for wakeup event

High bandwidth density per pin

Less congested board routing

Features

Benefits

Optimized transmit and receive queues

Network packets handled without waiting or buffer

overflow.

IEEE 802.3x compliant flow control support with software

controllable pause times and threshold values

Control over the transmissions of pause frames through

software or hardware triggering

Frame loss reduced from receive overruns

Caches up to 64 packet descriptors (per queue)

Efficient use of PCI Express bandwidth

Separate transmit queue per port

Efficient packet prioritization

Programmable host memory receive buffers (256 Bytes to

16 KBytes) and cache line size (64 Bytes to 128 Bytes)

Efficient use of PCI Express bandwidth

Wide, pipelined internal data path architecture

Low latency data handling

Superior DMA transfer rate performance

Dual 48 KByte configurable Transmit and Receive FIFO

buffers

No external FIFO memory requirements

FIFO size adjustable to application

Descriptor ring management hardware for transmit and

receive

Simple software programming model

Optimized descriptor fetching and write-back mechanisms

Efficient system memory and use of PCI Express

bandwidth

Mechanism available for reducing interrupts generated by

transmit and receive operations

Maximizes system performance and throughput

Supports transmission and reception of packets up to 9 kB

Enables jumbo frames

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 8257 | PROGRAMMABLE DMA CONTROLLER |

| 82586 | IEEE802.3 ETHERNET LAN COPROCESSOR |

| 82586-10 | IEEE802.3 ETHERNET LAN COPROCESSOR |

| 82586-6 | IEEE802.3 ETHERNET LAN COPROCESSOR |

| 82595FX | ISA BUS HIGH INTEGRATION ETHERNET CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 82573 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:GbE Controllers |

| 82-5730 | 制造商:TE Connectivity 功能描述: |

| 825732460 | 制造商:OMRON AUTOMATION AND SAFETY 功能描述:UM2460 UNIV MAT 5 M CBL TK1 SPEC |

| 82573-2460 | 制造商:OMRON AUTOMATION AND SAFETY 功能描述:UM2460 UNIV MAT 5 M CBL TK1 SPEC 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:UM5-2460-TK1 |

| 825732472 | 制造商:OMRON Industrial Automation 功能描述:UM2472 UNIV MAT 5 M CBL TK1 SPEC |

發(fā)布緊急采購,3分鐘左右您將得到回復。