- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382826 > 79RC32K438200BBI (INTEGRATED DEVICE TECHNOLOGY INC) IDTTM InterpriseTM Integrated Communications Processor PDF資料下載

參數(shù)資料

| 型號(hào): | 79RC32K438200BBI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | IDTTM InterpriseTM Integrated Communications Processor |

| 中文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA416 |

| 封裝: | 27 X 27 MM, PLASTIC, BGA-416 |

| 文件頁(yè)數(shù): | 12/59頁(yè) |

| 文件大小: | 644K |

| 代理商: | 79RC32K438200BBI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)

12 of 59

May 25, 2004

IDT 79RC32438

Pin Characteristics

Note:

Some input pads of the RC32438 do not contain internal pull-ups or pull-downs. Unused inputs should be tied off to appropriate

levels. This is especially critical for unused control signal inputs (such as BRN) which, if left floating, could adversely affect the RC32438’s

operation. Also, any input pin left floating can cause a slight increase in power consumption.

JTAG_TRST_N

I

JTAG Reset

. This active low signal asynchronously resets the boundary scan

logic, JTAG TAP Controller, and the EJTAG Debug TAP Controller. An external

pull-up on the board is recommended to meet the JTAG specification in cases

where the tester can access this signal. However, for systems running in func-

tional mode, one of the following should occur:

1) actively drive this signal low with control logic

2) statically drive this signal low with an external pull-down on the board

3) clock JTAG_TCK while holding EJTAG_TMS and/or JTAG_TMS high.

Debug

CPU

O

CPU Transaction.

This signal is asserted during all CPU instruction fetches and

data transfers to/from the DDR and devices on the memory and peripheral bus.

The signal is negated during PCI and DMA transactions to/from the DDR and

devices on the memory and peripheral bus.

INST

O

Instruction or Data.

This signal is driven high during CPU instruction fetches on

the memory and peripheral bus memory or DDR bus.

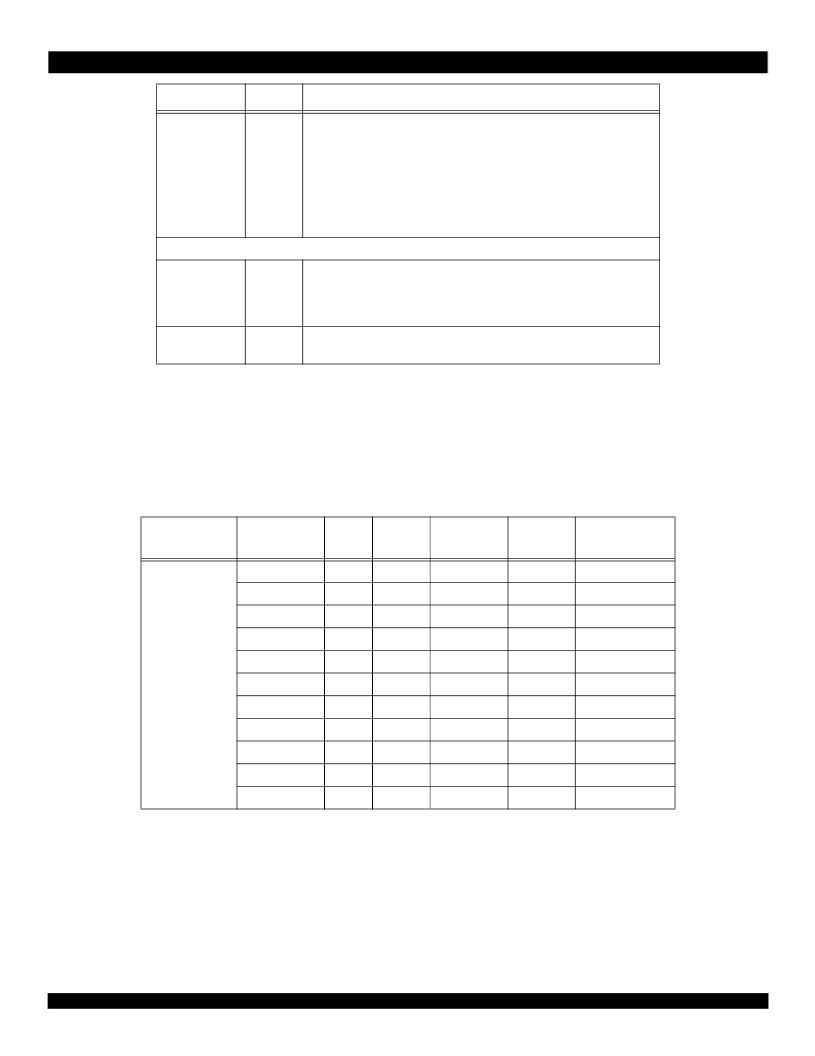

Function

Pin Name

Type

Buffer

I/O Type

Internal

Resistor

Notes

1

Memory and

Peripheral Bus

BDIRN

O

LVTTL

High Drive

BGN

O

LVTTL

Low Drive

BOEN

O

LVTTL

High Drive

BRN

I

LVTTL

STI

2

pull-up

BWEN[1:0]

O

LVTTL

High Drive

CSN[5:0]

O

LVTTL

High Drive

MADDR[21:0]

O

LVTTL

High Drive

MDATA[15:0]

I/O

LVTTL

High Drive

OEN

O

LVTTL

High Drive

RWN

O

LVTTL

High Drive

WAITACKN

I

LVTTL

STI

pull-up

Table 2 Pin Characteristics (Part 1 of 4)

Signal

Type

Name/Description

Table 1 Pin Description (Part 9 of 9)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 79RC32K438233BB | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438233BBI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438266BB | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438266BBI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438300BB | IDTTM InterpriseTM Integrated Communications Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC32K438-200BBI | 制造商:Integrated Device Technology Inc 功能描述:MPU RC32438 RISC 32-Bit 200MHz 2.5V/3.3V 416-Pin BGA 制造商:Integrated Device Technology Inc 功能描述:MPU RISC 32BIT 200MHZ 2.5V/3.3V 416BGA - Trays |

| 79RC32K438233BB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-233BB | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32K438-233BBG | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32K438-233BBGI | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。