- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382826 > 79RC32H435-350BCI (Integrated Device Technology, Inc.) IDTTM InterpriseTM Integrated Communications Processor PDF資料下載

參數(shù)資料

| 型號: | 79RC32H435-350BCI |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | IDTTM InterpriseTM Integrated Communications Processor |

| 中文描述: | IDTTM InterpriseTM集成通信處理器 |

| 文件頁數(shù): | 15/53頁 |

| 文件大?。?/td> | 444K |

| 代理商: | 79RC32H435-350BCI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

15 of 53

January 19, 2006

IDT 79RC32435

AC T iming Definitions

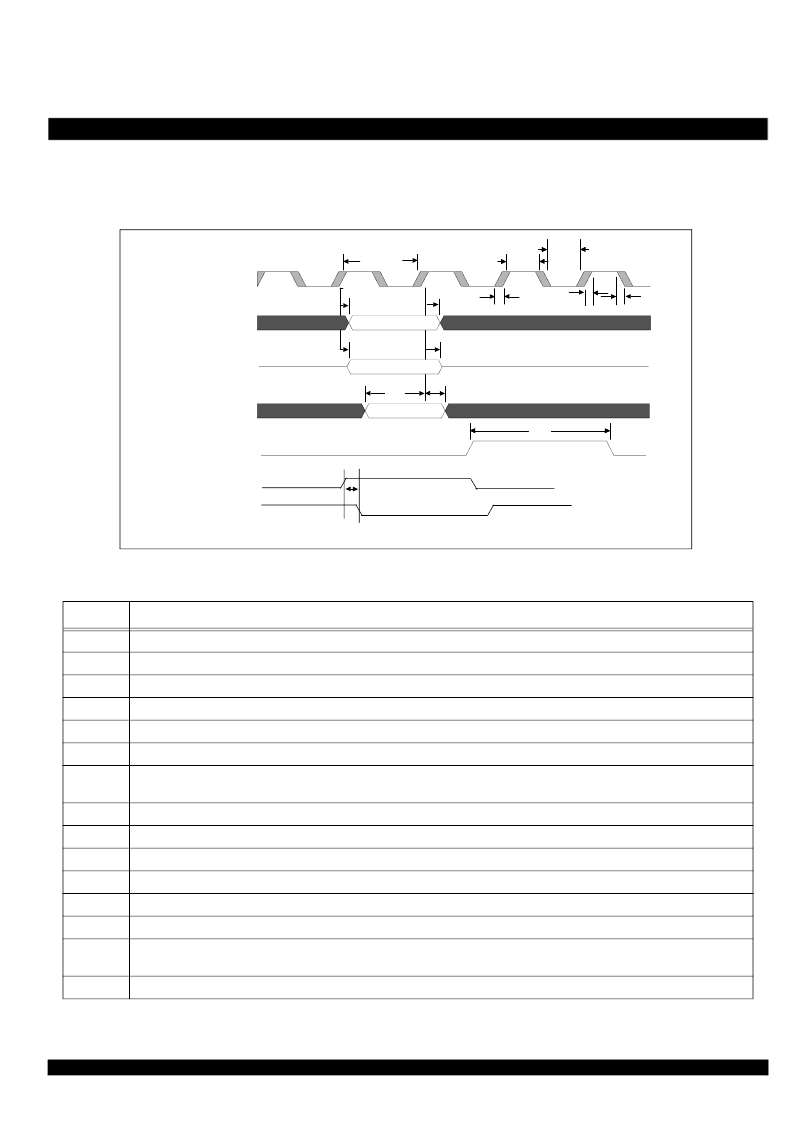

Below are examples of the AC timng characteristics used throughout this document.

Figure 2 AC Timing Definitions Waveform

S ymbol

Definition

Tper

Clock period.

Tlow

Clock low. Amount of time the clock is low in one clock period.

Thigh

Clock high. Amount of time the clock is high in one clock period.

Trise

Rise time. Low to high transition time.

Tfall

Fall time. High to low transition time.

Tjitter

Jitter. Amount of time the reference clock (or signal) edge can vary on either the rising or falling edges.

Tdo

Data out. Amount of time after the reference clock edge that the output will become valid. The mnimumtime represents the data output hold.

The maximumtime represents the earliest time the designer can use the data.

Tzd

Z state to data valid. Amount of time after the reference clock edge that the tri-stated output takes to become valid.

Tdz

Data valid to Z state. Amount of time after the reference clock edge that the valid output takes to become tri-stated.

Tsu

Input set-up. Amount of time before the reference clock edge that the input must be valid.

Thld

Input hold. Amount of time after the reference clock edge that the input must remain valid.

Tpw

Pulse width. Amount of time the input or output is active for asynchronous signals.

Tslew

Slew rate. The rise or fall rate for a signal to go froma high to low, or low to high.

X(clock)

Timng value. This notation represents a value of ‘X’ multiplied by the clock time period of the specified clock. Using 5(CLK) as an example:

X = 5 and the oscillator clock (CLK) = 25MHz, then the timng value is 200.

Tskew

Skew. The amount of time two signal edges deviate fromone another.

Table 4 AC Timing Definitions

Tdz

Tzd

Tdo

Tpw

Thld

Tsu

Tlow

Thigh

Tper

clock

Output signal 1

Output signal 2

Input Signal 1

Signal 1

Tjitter

Trise

Tfall

Tdo

Signal 2

Signal 3

Tskew

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 79RC32H435-400BC | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-400BCI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32438 | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-200BB | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-200BBI | IDTTM InterpriseTM Integrated Communications Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC32H435-400BC | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32H435-400BCG | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32H435-400BCI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438200BB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-200BB | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。