- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄360490 > 74LV74PWDH (NXP SEMICONDUCTORS) Dual D-type flip-flop with set and reset; positive-edge trigger PDF資料下載

參數(shù)資料

| 型號(hào): | 74LV74PWDH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 通用總線功能 |

| 英文描述: | Dual D-type flip-flop with set and reset; positive-edge trigger |

| 中文描述: | LV/LV-A/LVX/H SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 封裝: | PLASTIC, TSSOP1-14 |

| 文件頁(yè)數(shù): | 6/12頁(yè) |

| 文件大?。?/td> | 125K |

| 代理商: | 74LV74PWDH |

Philips Semiconductors

Product specification

74LV74

Dual D-type flip-flop with set and reset;

positive edge-trigger

1998 Apr 20

6

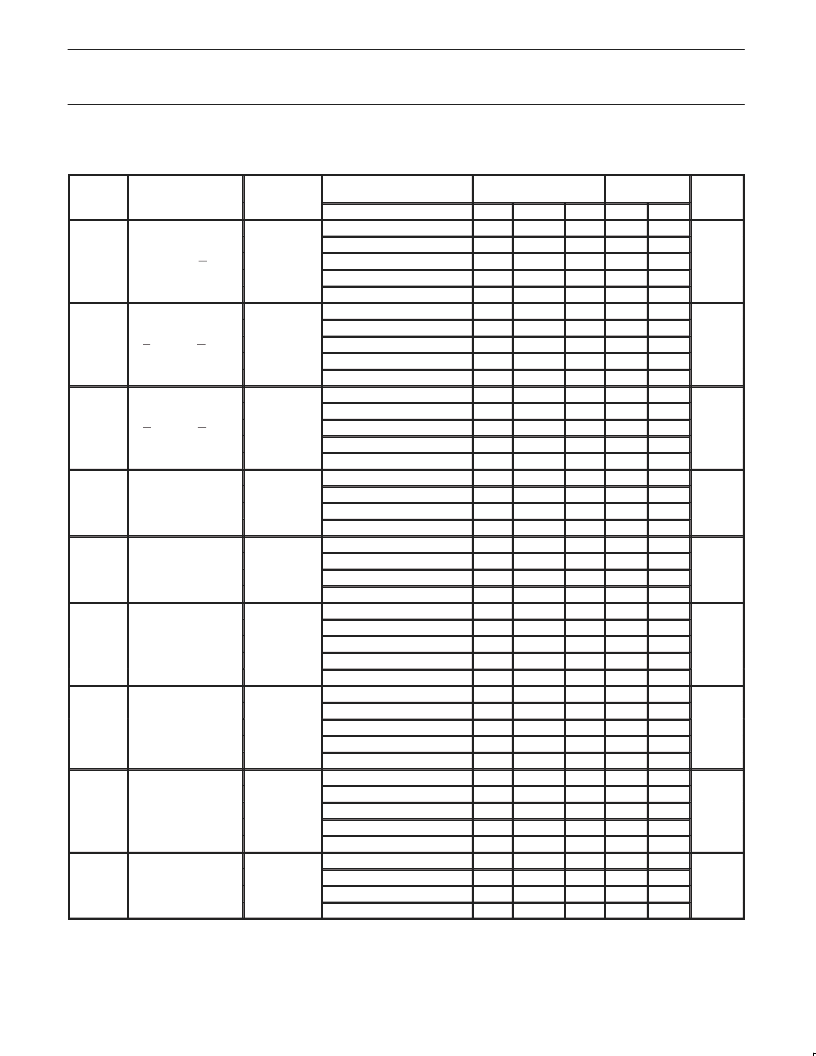

AC CHARACTERISTICS

GND = 0V; t

r

= t

f

2.5ns; C

L

= 50pF; R

L

= 1K

SYMBOL

PARAMETER

WAVEFORM

CONDITION

LIMITS

–40 to +85

°

C

TYP

1

70

24

18

13

2

9.5

3

90

31

23

17

2

12

3

90

31

23

17

2

12

3

10

8

7

2

6

3

10

8

7

2

6

3

5

2

1

1

2

1

3

10

4

3

2

2

1

2

–10

–2

–2

–2

2

–2

3

40

90

100

2

110

3

LIMITS

–40 to +125

°

C

MIN

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

41

30

24

18

41

30

24

18

–

15

11

9

7

–

26

15

10

8

–

3

3

3

3

12

40

48

56

UNIT

V

CC

(V)

1.2

2.0

2.7

3.0 to 3.6

4.5 to 5.5

1.2

2.0

2.7

3.0 to 3.6

4.5 to 5.5

1.2

2.0

2.7

3.0 to 3.6

4.5 to 5.5

2.0

2.7

3.0 to 3.6

4.5 to 5.5

2.0

2.7

3.0 to 3.6

4.5 to 5.5

1.2

2.0

2.7

3.0 to 3.6

4.5 to 5.5

1.2

2.0

2.7

3.0 to 3.6

4.5 to 5.5

1.2

2.0

2.7

3.0 to 3.6

4.5 to 5.5

2.0

2.7

3.0 to 3.6

4.5 to 5.5

MIN

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

34

25

20

15

34

25

20

15

–

14

10

8

6

–

22

12

8

6

–

3

3

3

3

14

50

60

70

MAX

–

44

28

26

17

–

46

34

27

19

–

46

34

27

19

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

MAX

–

56

41

33

23

–

58

43

34

24

–

58

43

34

24

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

Propagation delay

nCP to nQ, nQ

t

PHL/

t

PLH

Figures, 1, 3

ns

Propagation delay

nS

D

to nQ, nQ

t

PHL/

t

PLH

Figures 2, 3

ns

Propagation delay

nR

D

to nQ, nQ

t

PHL/

t

PLH

Figures 2, 3

ns

t

W

Clock pulse width

HIGH to LOW

Figure 1

ns

t

W

Set or reset pulse

width LOW

Figure 2

ns

Removal time

set or reset

t

rem

Figure 2

ns

Set up time

Set-up time

nD to nCP

t

su

Figure 1

ns

Hold time

nD to nCP

t

h

Figure 1

ns

f

max

Maximum clock

pulse frequency

Figure 1

MHz

NOTE:

1. Unless otherwise stated, all typical values are at T

amb

= 25

°

C.

2. Typical value measured at V

CC

= 3.3V.

3. Typical value measured at V

CC

= 5.0V.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LV86DB-T | Quad 2-input Exclusive OR (XOR) Gate |

| 74LV86D-T | Quad 2-input Exclusive OR (XOR) Gate |

| 74LV86PW-T | Quad 2-input Exclusive OR (XOR) Gate |

| 74LV86PWDH | Quad 2-input EXCLUSIVE-OR gate |

| 74LV86 | Quad 2-input EXCLUSIVE-OR gate(四2輸入異或門(mén)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LV74PW-Q100J | 制造商:NXP Semiconductors 功能描述:74LV74PW-Q100/TSSOP14/REEL13// - Tape and Reel 制造商:NXP Semiconductors 功能描述:IC FLIP-FLOP DUAL D POS 14TSSOP |

| 74LV74PW-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dual D-Type Flip-Flop |

| 74LV86 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Quad 2-input exclusive-OR gate |

| 74LV86AFPEL-E | 制造商:Renesas Electronics Corporation 功能描述:Cut Tape |

| 74LV86AS14-13 | 制造商:Diodes Incorporated 功能描述:LVA HIGH PIN COUNT SO-14 T&R 2.5K - Tape and Reel 制造商:Diodes Incorporated 功能描述:IC GATE XOR QUAD 2-IN 14SOIC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。