- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68813 > 73S8014BN-IL/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, PDSO20 PDF資料下載

參數(shù)資料

| 型號: | 73S8014BN-IL/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PDSO20 |

| 封裝: | ROHS COMPLIANT, SOP-20 |

| 文件頁數(shù): | 7/29頁 |

| 文件大?。?/td> | 345K |

| 代理商: | 73S8014BN-IL/F |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

DS_8014BN_057

73S8014BN Data Sheet

Rev. 1.0

15

3.2

System Controller Interface

Three digital inputs allow direct control of the card interface by the host. The 73S8014BN is controlled as follows:

Pin

CMDVCC: When asserted low, starts an activation sequence. When deasserted high, starts deactivation

sequence.

Pin RSTIN: Controls the card RST signal (when enabled by the sequencer) while the card is activated and the

power-down mode when the card is not activated.

Pin 5V/

3V: Defines the card V

DD voltage according to Table 8.

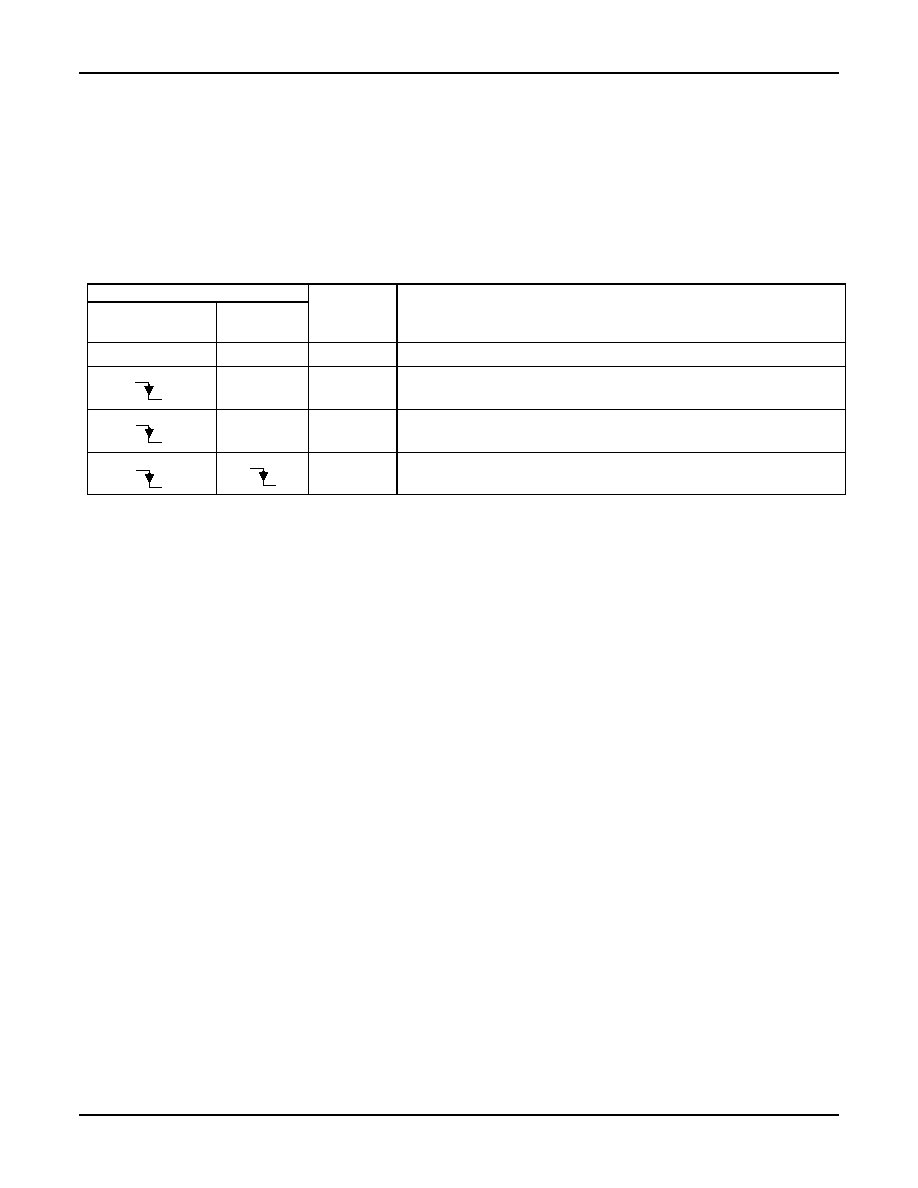

Table 8: VCC Voltage Logic Table

CONTROL PINS

VCC

VOLTAGE

(V)

NOTES

CMDVCC

5V/

3V

1

x

0

Off

1

5

5V/

3V must be stable for at least 1

s before assertion of

CMDVCC and held high until deassertion of CMDVCC.

0

3

5V/

3V must be stable for at least 1

s before assertion of

CMDVCC and held low until deassertion of CMDVCC.

1.8

Must be asserted low within 400ns of each other to generate

1.8V and held low until assertion of

CMDVCC.

The

OFF digital output reports status back to the host. See the Fault Detection and OFF section for details on the

operation of the

OFF output.

Note: 5V/

3V should not change during a card session. Doing so does not change the voltage on V

CC

during that session, but if it is changed, the 5V/

3V must be taken high outside the current card session

and before beginning the next card session. Otherwise, the next card session may not power up to the

selected VCC voltage.

3.3

Power-Down Mode

The 73S8014BN includes a power-down mode to greatly reduce the power consumption on the VDD and VPC

supplies when the smart card interface is deactivated. The power-down mode shuts down the crystal oscillator

and other internal circuits to save power. When the power-down mode is released, the oscillator is restarted. It

requires some time to start up and stabilize. During this time, the

OFF output goes low (if a card is inserted) and is

held low until the oscillator stabilizes, and then the

OFF output goes high to indicate that the device is ready to

activate the card.

The power-down mode is initiated when RSTIN,

CMDVCC, and 5V/3V are all logic-high for more than 2ms. The

power-down mode is released immediately by bringing RSTIN low. This action forces the

OFF output low for

approximately 5ms to 7ms to allow the oscillator to start up and stabilize. This action informs the host that the

73S8014BN is busy and should not be activated while the

OFF output is low. This ensures a proper activation

sequence after coming out of power-down.

The card-detection logic on the PRES input remains active in power-down mode. The card status is reported on

OFF.

Note: The

CMDVCC and 5V/3V inputs have no effect when exiting power-down. Bringing RSTIN low is the only

way to exit power-down.

Figure 4 shows the power-down mode control timing with PRES debounce. See Section 3.9 for a full description

of the PRES debounce behavior.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 73S8014RN-IL/F | SPECIALTY ANALOG CIRCUIT, PDSO20 |

| 73S8014RN-ILR/F | SPECIALTY ANALOG CIRCUIT, PDSO20 |

| 73S8023C-IM | SPECIALTY ANALOG CIRCUIT, QCC32 |

| 73S8023C-IM | SPECIALTY ANALOG CIRCUIT, QCC32 |

| 73S8023C-IMR | SPECIALTY ANALOG CIRCUIT, QCC32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73S8014BN-ILR/F | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Smart Card Interface |

| 73S8014R | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Smart Card Interface |

| 73S8014R-DB | 功能描述:界面開發(fā)工具 73S8014RRN/RT Demo Brd RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| 73S8014R-IL/F | 功能描述:I2C 接口集成電路 Smart Card Interface Comp w/8024 RoHS:否 制造商:NXP Semiconductors 電源電壓-最大:5.5 V 電源電壓-最小:2.3 V 最大工作頻率:400 KHz 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-16 |

| 73S8014R-IL/F1 | 功能描述:輸入/輸出控制器接口集成電路 RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。