- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360337 > 73M2910L-IG Microcontroller PDF資料下載

參數(shù)資料

| 型號: | 73M2910L-IG |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 18/41頁 |

| 文件大?。?/td> | 509K |

| 代理商: | 73M2910L-IG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

73M2910L

Microcontroller

HDLC STATUS REGISTER (HSTAT) SFR ADDRESS 0C3h

(continued)

18

BIT 4 RX Overrun

When bit 4 is set, a receive overrun condition has been detected. This is a condition where the HDLC has

received a new byte, but the last received data byte has not yet been read from the RX Data Register. As soon

as a new data byte has been received in an eight-bit serial register, it is loaded into the RX Data Register and a

new RX data interrupt is generated. If this interrupt is not serviced by reading the RX Data Register during the

time another new data byte is received, the RX overrun status bit will be set. The new received data will not

overwrite the older unread data.

Bit 4 will by cleared upon a reset and is cleared by a read of the HDLC Stat Register.

BIT 3 Invalid Flag

When bit 3 is set, an invalid flag has been detected. This is a condition where a 7E pattern with no inserted 0s is

detected, and this pattern did not originate on a byte boundary. Note, two consecutive flags may share a 0, so

that the second (or subsequent) flag may not appear to be on a byte boundary. This condition does not result in

an invalid flag indication.

Bit 3 will by cleared upon a reset and is cleared by a read of the HDLC Stat Register.

BIT 2 Abort Detect

When bit 2 is set, an abort condition has been detected. This is a condition where seven consecutive ones, with

no inserted zeros, are received after an active state. Bit 2 will be cleared upon a reset and is cleared by a read

of the HDLC Stat Register.

BIT 1 Idle Detect

When bit 1 is set, the first indication of an idle state is detected. An idle state is declared when 15 consecutive

ones, with no inserted zeros, are received after an active state.

Bit 1 will be cleared upon a reset and is cleared by a read of the HDLC Stat Register.

BIT 0 Flag Detect

When bit 0 is set, the HDLC has received a 7E pattern with no inserted 0’s. Bit 0 will by cleared upon a reset

and is cleared by a read of the HDLC Stat Register.

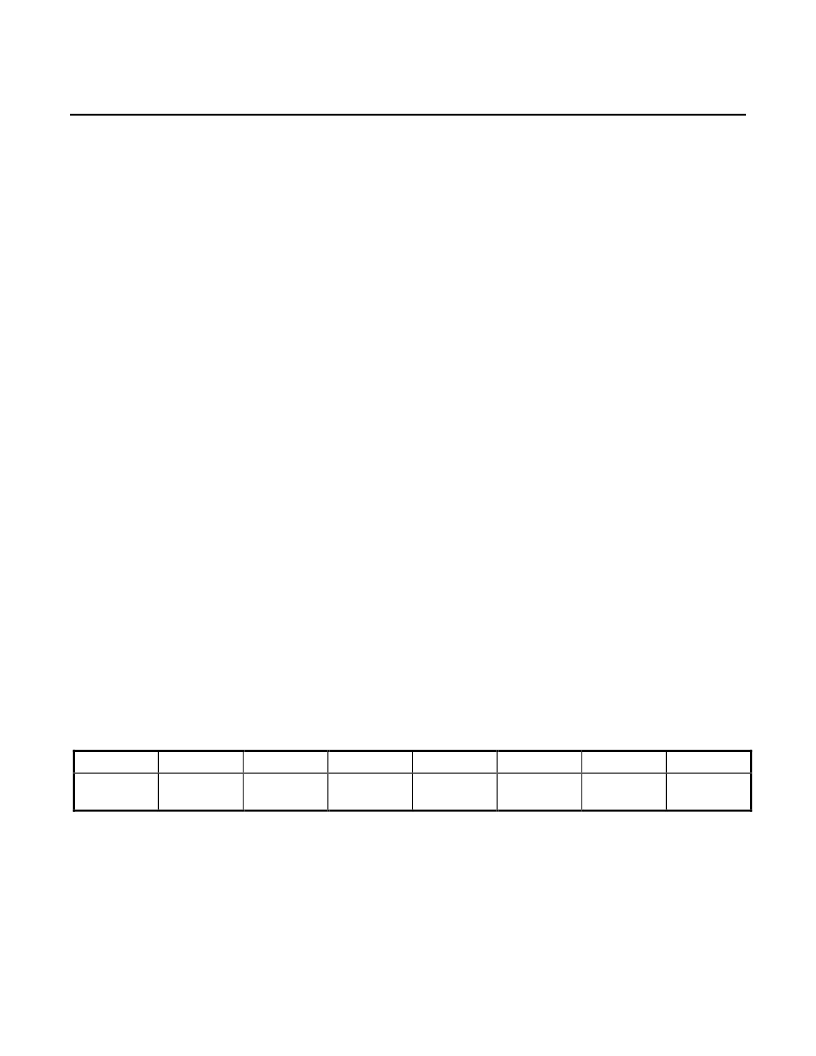

HDLC INTERRUPT ENABLE REGISTER (HIE) SFR ADDRESS 0C4h

Byte Addressable

Reset State 00h

If the bit is set, the corresponding interrupt source is enabled.

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

TX RDY

IE

RX RDY

IE

TX RDY

EN

RX RDY

EN

INVAL

FLG IE

ABORT

IE

IDLE

IE

FLAG

IE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 73S1121F | 10-Bit Bus LVDS Deserializers |

| 74-4900 | TUERSCHLIESSER KRAFT EINSTELLBAR 1/5 |

| 74-5700 | High-Speed, Low-Power, 3V/5V, Rail-to-Rail, Single-Supply Comparators |

| 74-6700 | High-Speed, Low-Power, 3V/5V, Rail-to-Rail, Single-Supply Comparators |

| 7400041(A4) | 10-Bit, Bus LVDS Serializers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73M2921 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Advanced Single Chip Modem |

| 73M2921-IG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Advanced Single Chip Modem |

| 73M2AR0015F | 功能描述:RES 0.0015 OHM 1% 2W 2512 制造商:cts resistor products 系列:73M2A 包裝:帶卷(TR) 零件狀態(tài):在售 電阻值:1.5 MOhms 容差:±1% 功率(W):2W 成分:金屬薄膜 特性:電流檢測 溫度系數(shù):±100ppm/°C 工作溫度:-55°C ~ 155°C 封裝/外殼:2512(6432 公制) 供應(yīng)商器件封裝:2512 大小/尺寸:0.248" 長 x 0.126" 寬(6.30mm x 3.20mm) 高度 - 安裝(最大值):0.043"(1.10mm) 端子數(shù):2 故障率:- 標(biāo)準(zhǔn)包裝:4,000 |

| 73M2AR001F | 功能描述:RES 0.001 OHM 1% 2W 2512 制造商:cts resistor products 系列:73M2A 包裝:帶卷(TR) 零件狀態(tài):在售 電阻值:1 MOhms 容差:±1% 功率(W):2W 成分:金屬薄膜 特性:電流檢測 溫度系數(shù):±100ppm/°C 工作溫度:-55°C ~ 155°C 封裝/外殼:2512(6432 公制) 供應(yīng)商器件封裝:2512 大小/尺寸:0.248" 長 x 0.126" 寬(6.30mm x 3.20mm) 高度 - 安裝(最大值):0.043"(1.10mm) 端子數(shù):2 故障率:- 標(biāo)準(zhǔn)包裝:4,000 |

| 73M2AR0025F | 功能描述:RES 0.0025 OHM 1% 2W 2512 制造商:cts resistor products 系列:73M2A 包裝:帶卷(TR) 零件狀態(tài):在售 電阻值:2.5 mOhms 容差:±1% 功率(W):2W 成分:金屬薄膜 特性:電流檢測 溫度系數(shù):±100ppm/°C 工作溫度:-55°C ~ 155°C 封裝/外殼:2512(6432 公制) 供應(yīng)商器件封裝:2512 大小/尺寸:0.248" 長 x 0.126" 寬(6.30mm x 3.20mm) 高度 - 安裝(最大值):0.043"(1.10mm) 端子數(shù):2 故障率:- 標(biāo)準(zhǔn)包裝:4,000 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。