- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68811 > 71M6532D-IGT/F (MAXIM INTEGRATED PRODUCTS INC) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | 71M6532D-IGT/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 封裝: | LEAD FREE, LQFP-100 |

| 文件頁數(shù): | 65/120頁 |

| 文件大?。?/td> | 2477K |

| 代理商: | 71M6532D-IGT/F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當(dāng)前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁

FDS 6531/6532 005

Data Sheet 71M6531D/F-71M6532D/F

v1.3

2005-2010 TERIDIAN Semiconductor Corporation

49

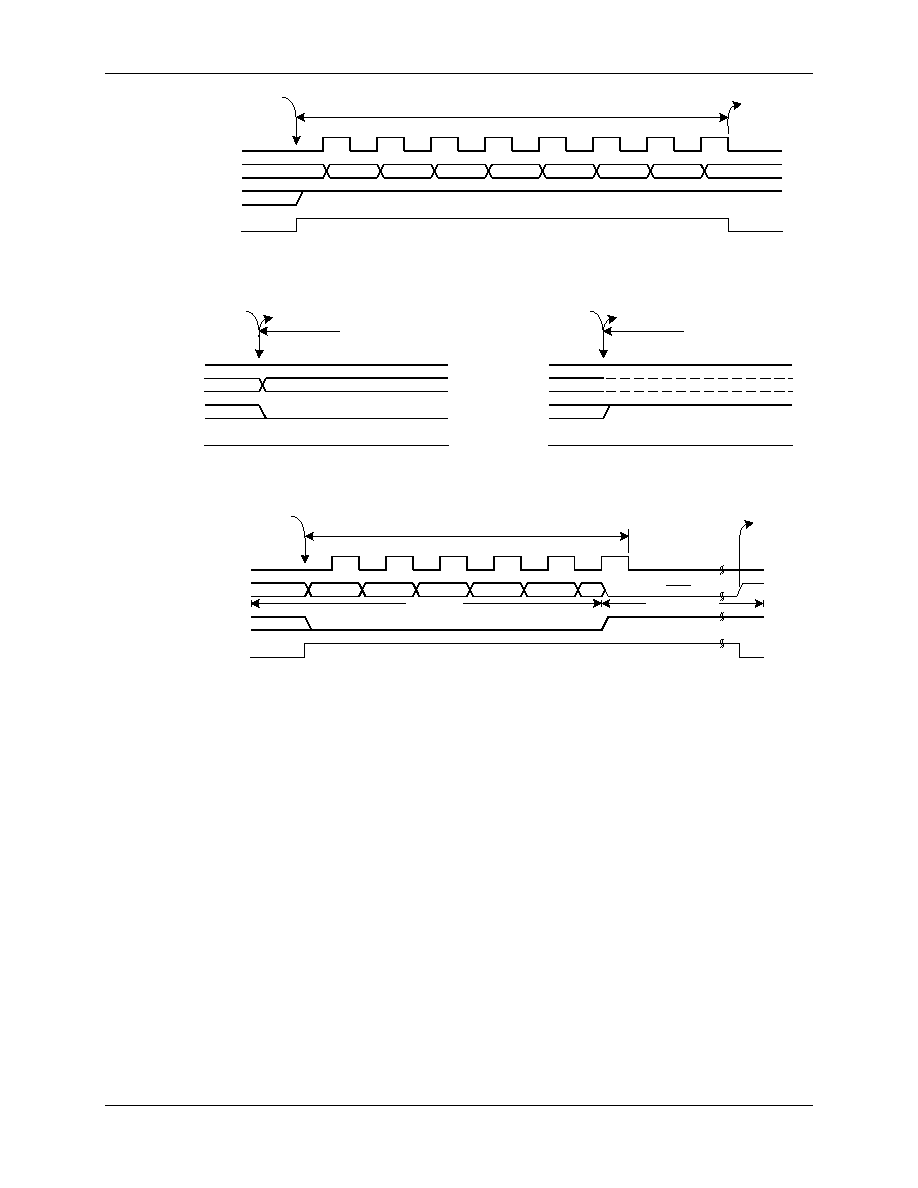

Figure 13: 3-Wire Interface. Read Command.

Figure 14: 3-Wire Interface. Write Command when CNT=0

Figure 15: 3-Wire Interface. Write Command when HiZ=1 and WFR=1

1.5.15 SPI Slave Port

The slave SPI port communicates directly with the MPU data bus and is able to read and write Data RAM

locations. It is also able to send commands to the MPU. The interface to the slave port consists of the

PCSZ, PCLK, PSDI and PSDO pins. These pins are multiplexed with the LCD segment driver pins SEG3

to SEG6. The port pins default to LCD driver pins. The port is enabled by setting the SPE bit.

A typical SPI transaction is as follows. While PCSZ is high, the port is held in an initialized/reset state.

During this state, PSDO is held in HiZ state and all transitions on PCLK and PSDI are ignored. When

PCSZ falls, the port will begin the transaction on the first rising edge of PCLK. A transaction consists of

an 8-bit command, a 16-bit address and then one or more bytes of data. The transaction ends when

PCSZ is raised. Some transactions may consist of a command only.

The last SPI command and address (if part of the command) are available to the MPU in registers

SP_CMD and SP_ADDR.

The SPI port supports data transfers at 1 Mb/s in mission mode and 16 kb/s in brownout mode. The SPI

commands are described in Table 49 and in Figure 16 illustrate the SPI Interface read and write timing.

CNT Cycles (8 shown)

READ

D0

D1

D2

D3

D4

D5

INT5

D6

D7

EECTRL Byte Written

SCLK (output)

BUSY (bit)

SDATA (input)

SDATA output Z

(HiZ)

CNT Cycles (0 shown)

Write -- No HiZ

D7

INT5 not issued

CNT Cycles (0 shown)

Write -- HiZ

INT5 not issued

EECTRL Byte Written

SCLK (output)

BUSY (bit)

SDATA (output)

SCLK (output)

BUSY (bit)

SDATA (output)

(HiZ)

SDATA output Z

(LoZ)

CNT Cycles (6 shown)

Write -- With HiZ and WFR

EECTRL Byte Written

SCLK (output)

BUSY (bit)

SDATA (out/in)

D2

D3

D4

D5

D6

D7

BUSY

READY

(From EEPROM)

INT5

(From 6520)

SDATA output Z

(HiZ)

(LoZ)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71M6531D-IMR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 71M6532F-IGTR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6532D-IGT/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6531D-IM/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 71M6532F-IGTR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71M6532D-IGTR/F | 功能描述:計(jì)量片上系統(tǒng) - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6532D-IGTR/F1 | 功能描述:計(jì)量片上系統(tǒng) - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6532F | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Energy Meter IC |

| 71M6532F-IGT/F | 功能描述:計(jì)量片上系統(tǒng) - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6532F-IGT/F1 | 功能描述:計(jì)量片上系統(tǒng) - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。