- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68811 > 71M6531D-IM/F (TERIDIAN SEMICONDUCTOR CORP) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 PDF資料下載

參數(shù)資料

| 型號(hào): | 71M6531D-IM/F |

| 廠商: | TERIDIAN SEMICONDUCTOR CORP |

| 元件分類: | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 封裝: | LEAD FREE, QFN-68 |

| 文件頁(yè)數(shù): | 13/120頁(yè) |

| 文件大?。?/td> | 2477K |

| 代理商: | 71M6531D-IM/F |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)

FDS 6531/6532 005

Data Sheet 71M6531D/F-71M6532D/F

v1.3

2005-2010 TERIDIAN Semiconductor Corporation

11

1.2.2

Input Multiplexer

The input multiplexer supports up to four input signals that are applied to pins IA (IAP/IAN), VA, IB

(IBP/IBN), and VB of the device. Additionally, using the alternate multiplexer selection, it has the ability to

select temperature and the battery voltage. The multiplexer can be operated in two modes:

During a normal multiplexer cycle, the signals from the IA (IAP/IAN), IB (IBP/IBN), VA and VB pins

are selected.

During the alternate multiplexer cycle, the temperature signal (TEMP) and the battery monitor are

selected, along with some of the voltage and/or current signal sources shown in Table 1. To prevent

unnecessary drainage on the battery, the battery monitor is only active when enabled with the BME

bit (0x2020[6]) in the I/O RAM.

The alternate multiplexer cycles are usually performed infrequently (every second or so) by the MPU. In

order to prevent disruption of the voltage tracking PLL and voltage allpass networks, VA is not replaced in

the ALT selections. Table 1 details the regular and alternative multiplexer sequences. The computation

engine (CE) fills in missing samples due to an ALT multiplexer sequence.

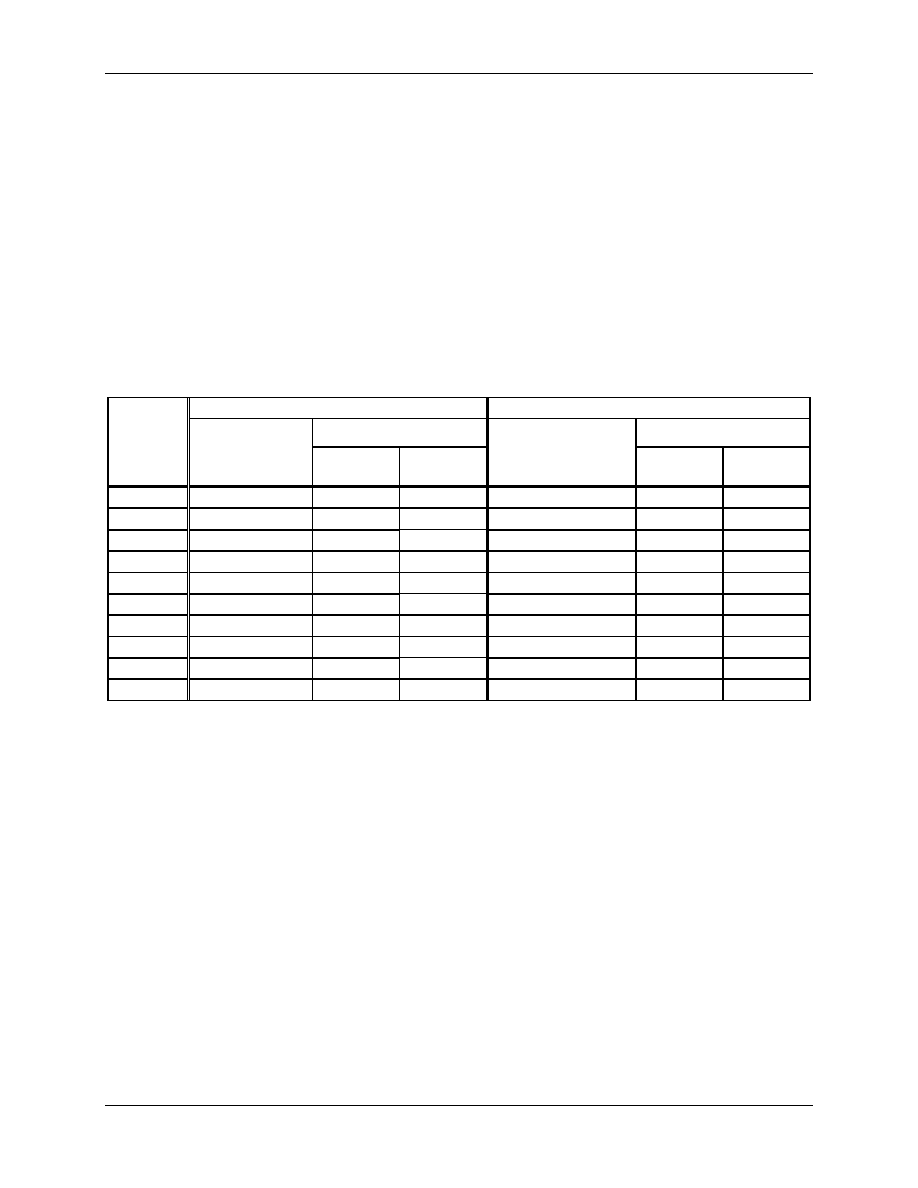

Table 1: Inputs Selected in Regular and Alternate Multiplexer Cycles

Time

Slot

Regular Slot

Alternate Slot

Register

Typical Selections

Register

Typical Selections

RAM

Address

Signal for

ADC

RAM

Address

Signal for

ADC

0

SLOT0_SEL[3:0]

0

IA

SLOT0_ALTSEL[3:0]

A

TEMP

1

SLOT1_SEL[3:0]

1

VB

SLOT1_ALTSEL[3:0]

1

VB

2

SLOT2_SEL[3:0]

2

IB

SLOT2_ALTSEL[3:0]

B

VBAT

3

SLOT3_SEL[3:0]

3

VA

SLOT3_ALTSEL[3:0]

3

VA

–

SLOT4_SEL[3:0]

–

SLOT4_ALTSEL[3:0]

–

SLOT5_SEL[3:0]

–

SLOT5_ALTSEL[3:0]

–

SLOT6_SEL[3:0]

–

SLOT6_ALTSEL[3:0]

–

SLOT7_SEL[3:0]

–

SLOT7_ALTSEL[3:0]

–

SLOT8_SEL[3:0]

–

SLOT8_ALTSEL[3:0]

–

SLOT9_SEL[3:0]

–

SLOT9_ALTSEL[3:0]

–

The sequence of sampled channels is fully programmable using I/O RAM registers. SLOTn_SEL[3:0]

selects the input for the nth state in a standard multiplexer frame, while SLOTn_ALTSEL[3:0] selects the

input for the nth state in an alternate multiplexer frame. The states shown in Table 1 are examples for

possible multiplexer state sequences.

In a typical application, IA (IAN/IAP) and IB (IBN/IBP) are connected to current transformers that sense

the current on each phase of the line voltage. VA and VB are typically connected to voltage sensors

through resistor dividers.

The multiplexer control circuit (MUX_CTRL signal) controls multiplexer advance, FIR initiation and VREF

chopping. Additionally, MUX_CTRL launches each pass through the CE program. Conceptually,

MUX_CTRL is clocked by CK32, the 32768 Hz clock from the PLL block. The behavior of MUX_CTRL is

governed by MUX_ALT, EQU[2:0], CHOP_E[1:0] and MUX_DIV[3:0].

The MUX_ALT bit requests an alternative multiplexer frame. The bit may be asserted on any MPU cycle

and may be subsequently de-asserted on any cycle including the next one. A rising edge on MUX_ALT

will cause MUX_CTRL to wait until the next multiplexer frame and implement a single alternate multiplexer

frame.

Another control input to the MUX is MUX_DIV[3:0]. These four bits can request from 1 to 10 multiplexer

states per frame. The multiplexer always starts at the beginning of its list and proceeds until the number

of states defined by MUX_DIV[3:0] have been converted.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71M6532F-IGTR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6534-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6534H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71M6531D-IMR/F | 功能描述:計(jì)量片上系統(tǒng) - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6531D-IMR/F1 | 功能描述:計(jì)量片上系統(tǒng) - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6531D-IMR/F2 | 功能描述:計(jì)量片上系統(tǒng) - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6531F | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Energy Meter IC |

| 71M6531F-DB | 功能描述:開發(fā)板和工具包 - 8051 71M6531F Demo Brd RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評(píng)估:C8051F960, Si7005 核心: 接口類型:USB 工作電源電壓: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。