- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄294088 > 70V25S15PFG (INTEGRATED DEVICE TECHNOLOGY INC) 8K X 16 DUAL-PORT SRAM, 15 ns, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | 70V25S15PFG |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 8K X 16 DUAL-PORT SRAM, 15 ns, PQFP100 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, GREEN, PLASTIC, TQFP-100 |

| 文件頁(yè)數(shù): | 3/25頁(yè) |

| 文件大?。?/td> | 211K |

| 代理商: | 70V25S15PFG |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

6.42

11

IDT70V35/34S/L (IDT70V25/24S/L)

High-Speed 3.3V 8/4K x 18 (8/4K x 16) Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

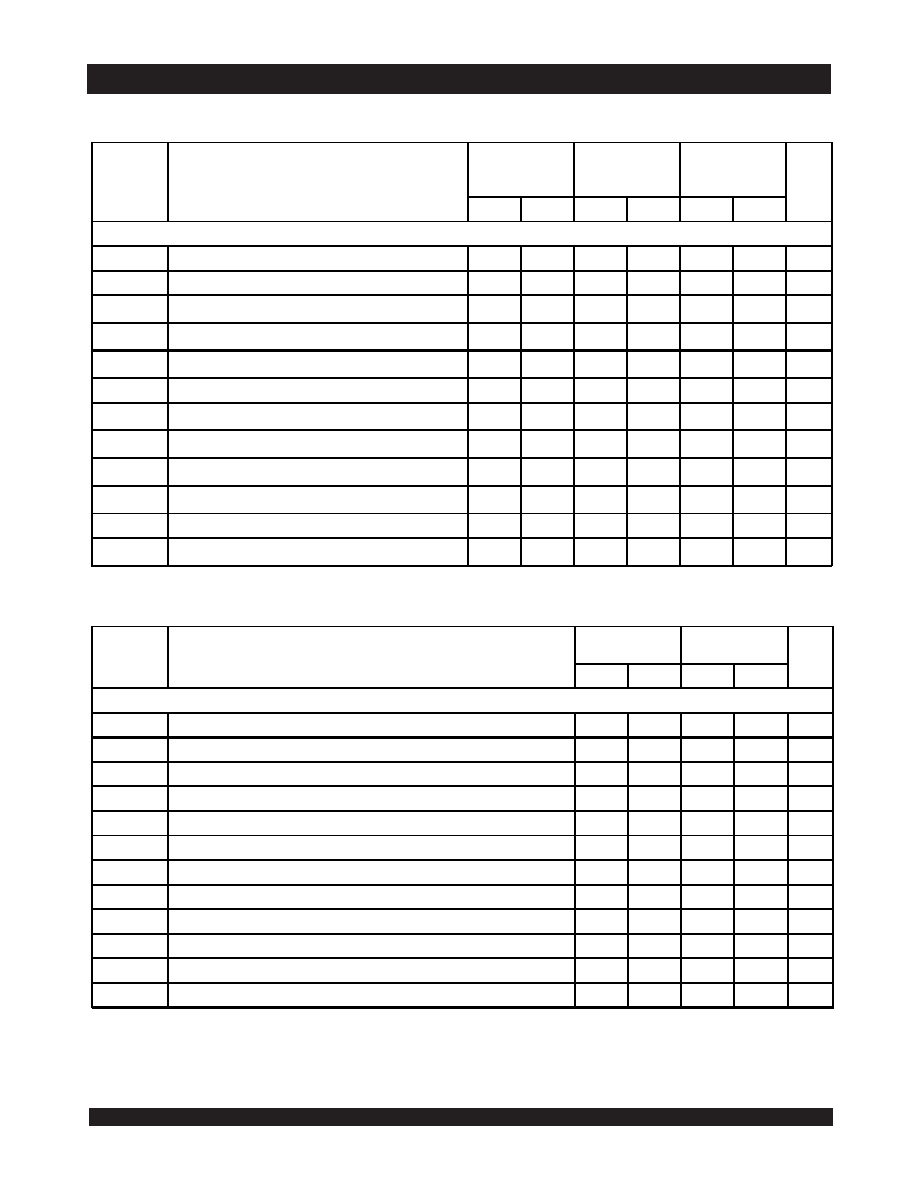

AC Electrical Characteristics Over the Operating

Temperature and Supply Voltage Range for 70V25/24(4)

NOTES:

1. Transition is measured 0mV from Low or High-impedance voltage with Output Test Load (Figure 2).

2. This parameter is guaranteed by device characterization, but is not production tested.

3. To access RAM,

CE = VIL, UB or LB = VIL, and SEM = VIH. To access semaphore, CE = VIH or UB & LB = VIH, and SEM = VIL.

4. 'X' in part number indicates power rating (S or L).

70V25/24X15

Com'l Only

70V25/24X20

Com'l

& Ind

70V25/24X25

Com'l

& Ind

Unit

Symbol

Parameter

Min.

Max.Min.Max.Min.Max.

READ CYCLE

tRC

Read Cycle Time

15

____

20

____

25

____

ns

tAA

Address Access Time

____

15

____

20

____

25

ns

tACE

Chip Enable Access Time

(3)

____

15

____

20

____

25

ns

tABE

Byte Enable Access Time(3)

____

15

____

20

____

25

ns

tAOE

Output Enable Access Time(3)

____

10

____

12

____

13

ns

tOH

Output Hold from Address Change

3

____

3

____

3

____

ns

tLZ

Output Low-Z Time(1,2)

3

____

3

____

3

____

ns

tHZ

Output High-Z Time(1,2)

____

10

____

12

____

15

ns

tPU

Chip Enable to Power Up Time(1,2)

0

____

0

____

0

____

ns

tPD

Chip Disable to Power Down Time

(1,2)

____

15

____

20

____

25

ns

tSOP

Semaphore Flag Update Pulse (

OE or SEM)10

____

10

____

10

____

ns

tSAA

Semaphore Address Access(3)

____

15

____

20

____

25

ns

5624 tbl 11a

70V25/24X35

Com'l Only

70V25/24X55

Com'l Only

Unit

Symbol

Parameter

Min.

Max.

Min.

Max.

READ CYCLE

tRC

Read Cycle Time

35

____

55

____

ns

tAA

Address Access Time

____

35

____

55

ns

tACE

Chip Enable Access Time

(3)

____

35

____

55

ns

tABE

Byte Enable Access Time(3)

____

35

____

55

ns

tAOE

Output Enable Access Time(3)

____

20

____

30

ns

tOH

Output Hold from Address Change

3

____

3

____

ns

tLZ

Output Low-Z Time(1,2)

3

____

3

____

ns

tHZ

Output High-Z Time

(1,2)

____

15

____

25

ns

tPU

Chip Enable to Power Up Time(1,2)

0

____

0

____

ns

tPD

Chip Disable to Power Down Time(1,2)

____

35

____

50

ns

tSOP

Semaphore Flag Update Pulse (

OE or SEM)15

____

15

____

ns

tSAA

Semaphore Address Access(3)

____

35

____

55

ns

5624 tbl 11b

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 70V25L25PFGI | 8K X 16 DUAL-PORT SRAM, 25 ns, PQFP100 |

| 70V34S20PFGI | 4K X 18 DUAL-PORT SRAM, 20 ns, PQFP100 |

| 710-405J12 | STEEL, CIRCULAR ADAPTER |

| 710-405J16 | STEEL, CIRCULAR ADAPTER |

| 710-405J24 | STEEL, CIRCULAR ADAPTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 70V25S20J | 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 128KBIT 8KX16 20NS 84PLCC - Rail/Tube |

| 70V25S20J8 | 功能描述:IC SRAM 128KBIT 20NS 84PLCC 制造商:idt, integrated device technology inc 系列:- 包裝:帶卷(TR) 零件狀態(tài):有效 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SRAM - 雙端口,異步 存儲(chǔ)容量:128K(8K x 16) 速度:20ns 接口:并聯(lián) 電壓 - 電源:3 V ~ 3.6 V 工作溫度:0°C ~ 70°C(TA) 封裝/外殼:84-LCC(J 形引線) 供應(yīng)商器件封裝:84-PLCC(29.21x29.21) 標(biāo)準(zhǔn)包裝:200 |

| 70V25S20PF | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 8Kx16, 3.3V DUAL- PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V25S20PF8 | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 8Kx16, 3.3V DUAL- PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V25S25G | 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 128KBIT 8KX16 25NS 84PIN PGA - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。