- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄296206 > 70V05L35PF (INTEGRATED DEVICE TECHNOLOGY INC) 8K X 8 DUAL-PORT SRAM, 35 ns, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | 70V05L35PF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | SRAM |

| 英文描述: | 8K X 8 DUAL-PORT SRAM, 35 ns, PQFP64 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, TQFP-64 |

| 文件頁(yè)數(shù): | 3/22頁(yè) |

| 文件大小: | 159K |

| 代理商: | 70V05L35PF |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

6.42

IDT70V05S/L

High-Speed 3.3V 8K x 8 Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

11

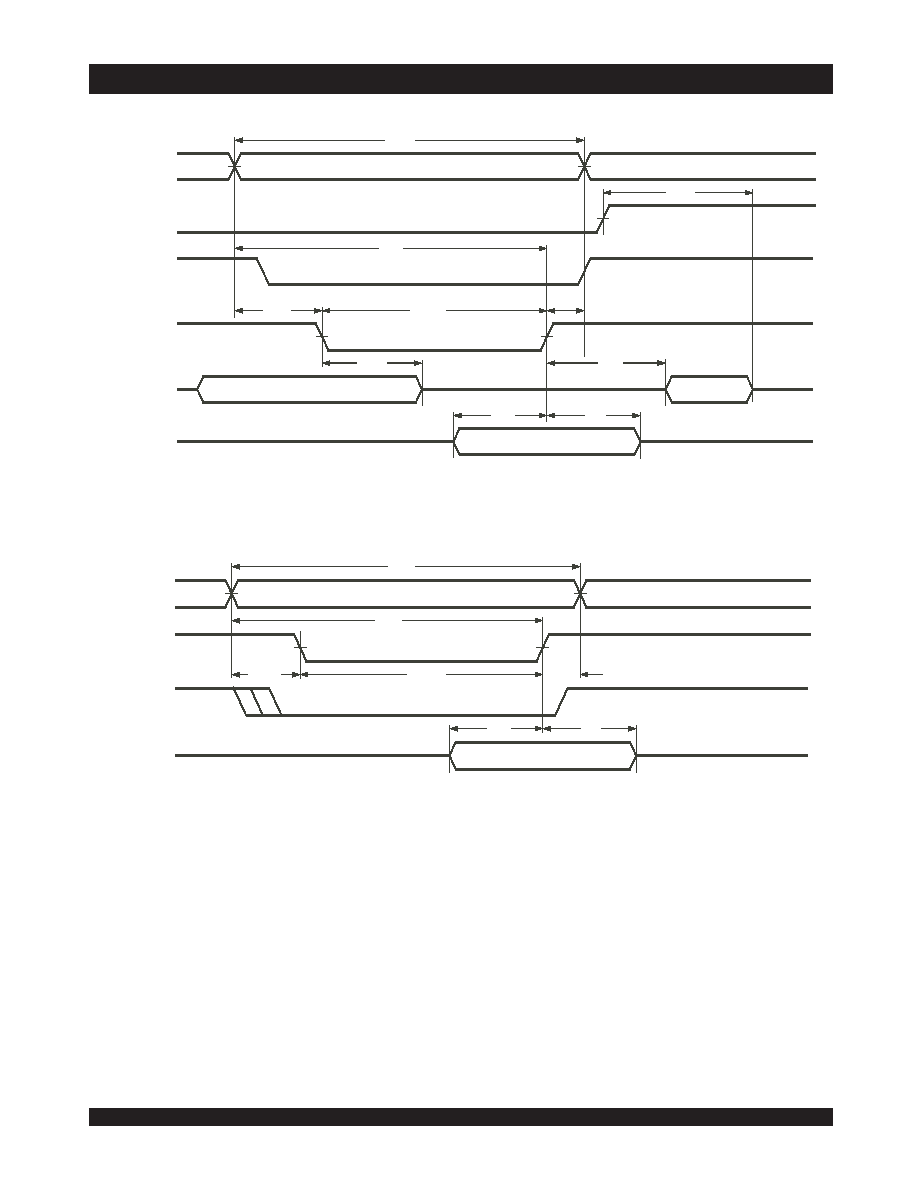

Timing Waveform of Write Cycle No. 1, R/W Controlled Timing(1,3,5,8)

NOTES:

1. R/W or CE must be HIGH during all address transitions.

2. A write occurs during the overlap (tEW or tWP) of a LOW CE and a LOW R/W for memory array writing cycle.

3. tWR is measured from the earlier of CE or R/W (or SEM or R/W) going HIGH to the end of write cycle.

4. During this period, the I/O pins are in the output state and input signals must not be applied.

5. If the CE or SEM LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the High-impedance state.

6. Timing depends on which enable signal is asserted last, CE, or R/W.

7. Timing depends on which enable signal is de-asserted first, CE, or R/W.

8. If OE is LOW during R/W controlled write cycle, the write pulse width must be the larger of tWP or (tWZ + tDW) to allow the I/O drivers to turn off and data to be placed on the

bus for the required tDW. If OE is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified tWP.

9. To access RAM, CE = VIL and SEM = VIN. To access Semaphore, CE = VIH and SEM = VIL. tEW must be met for either condition.

Timing Waveform of Write Cycle No. 2, CE Controlled Timing(1,3,5,8)

2941 drw 09

tWC

tAS

tWR

tDW

tDH

ADDRESS

DATAIN

CE or SEM

R/

W

tAW

tEW

(3)

(2)

(6)

(9)

R/

W

tWC

tHZ

tAW

tWR

tAS

tWP

DATAOUT

(2)

tWZ

tDW

tDH

tOW

OE

ADDRESS

DATAIN

CE

(6)

(4)

(3)

2941 drw 08

(7)

or

SEM

(9)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 70V05S15J8 | 8K X 8 DUAL-PORT SRAM, 15 ns, PQCC68 |

| 70V05S55G | 8K X 8 DUAL-PORT SRAM, 55 ns, CPGA68 |

| 70V05S55J8 | 8K X 8 DUAL-PORT SRAM, 55 ns, PQCC68 |

| IDT71502L55CB | 4K X 16 STANDARD SRAM, 25 ns, CDIP48 |

| IDT71B65S20TDB | 8K X 8 STANDARD SRAM, 20 ns, CDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 70V05L35PF8 | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 8K x 8 3.3v Dual- Port Ram RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V05L35PFI | 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 64KBIT 8KX8 35NS 64TQFP - Bulk |

| 70V05L35PFI8 | 功能描述:IC SRAM 64KBIT 64TQFP 制造商:idt, integrated device technology inc 系列:* 零件狀態(tài):最後搶購(gòu) 標(biāo)準(zhǔn)包裝:750 |

| 70V05L55G | 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 64KBIT 8KX8 55NS 68PIN PGA - Trays |

| 70V05L55J | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 8K x 8 3.3v Dual- Port Ram RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。