- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67347 > 5962-9865901HXA (ANALOG DEVICES INC) DUAL 3-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 PDF資料下載

參數(shù)資料

| 型號: | 5962-9865901HXA |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | DUAL 3-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 封裝: | CERAMIC, LCC-68 |

| 文件頁數(shù): | 2/24頁 |

| 文件大小: | 2403K |

| 代理商: | 5962-9865901HXA |

AD10265

–10–

REV. A

THEORY OF OPERATION

Refer to the Functional Block Diagram. The AD10265 employs

three monolithic ADI components per channel (AD9631,

AD9632, and AD6640), along with multiple passive resistor

networks and decoupling capacitors to fully integrate a complete

12-bit analog-to-digital converter.

The input signal is first passed through a precision laser-trimmed

resistor divider, allowing the user to externally select operation

with a full-scale signal of

±0.5 V, ±1.0 V, or ±2.0 V by choosing

the proper input terminal for the application.

Since the AD6640 implements a true differential analog input,

the AD9631/AD9632 have been configured to provide a differ-

ential input for the AD6640 ADC through ac-coupling. The ac

signal gain of the AD9631/AD9632 can be trimmed to provide a

constant differential input to the AD6640. This allows the

converter to be used in multiple system applications without

the need for external gain circuit normally requiring trim. The

AD9631/AD9632 were chosen for their superior ac performance

and input drive capabilities, which have limited the ability of

many amplifiers to drive high-performance ADCs. As new

amplifiers are developed, pin-compatible improvements are

planned to incorporate the latest operational amplifier technology.

APPLYING THE AD10265

Encoding the AD10265

Best performance is obtained by driving the encode pins differ-

entially. However, the AD10265 is also designed to interface

with TTL and CMOS logic families. The source used to drive

the ENCODE pin(s) must be clean and free from jitter. Sources

with excessive jitter will limit SNR and overall performance.

0.01 F

TTL OR CMOS

SOURCE

ENCODE

AD10265

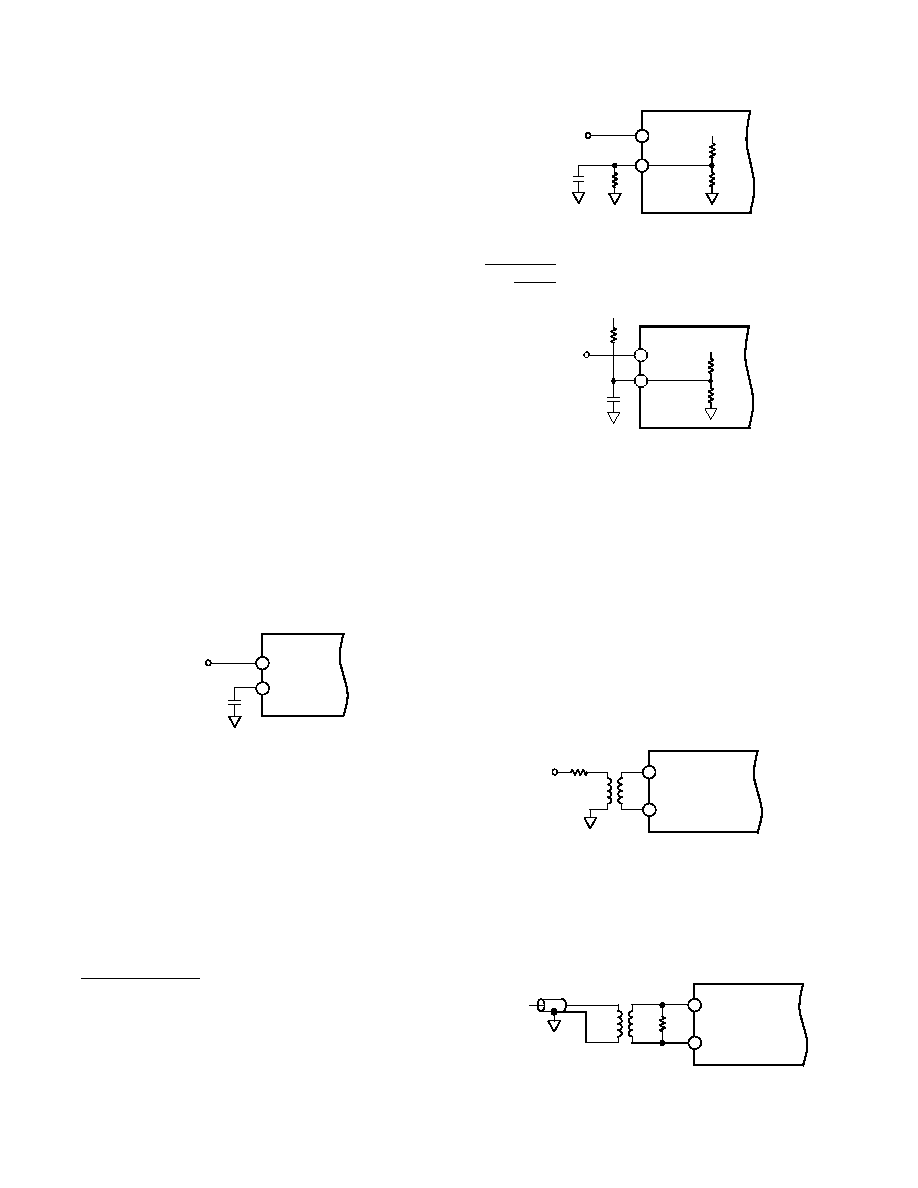

Figure 6. Single-Ended TTL/CMOS Encode

The AD10265 encode inputs are connected to a differential input

stage (see Figure 4 under Equivalent Circuits). With no input

connected to either ENCODE pin, the voltage divider biases the

inputs to 1.6 V. For TTL or CMOS usage, the encode source

should be connected to ENCODE.

ENCODE should be

decoupled using a low inductance or microwave chip capacitor

to ground.

If a logic threshold other than the nominal 1.6 V is required,

the following equations show how to use an external resistor,

Rx, to raise or lower the trip point (see Figure 4, R1 = 17 k

,

R2 = 8 k

).

V

RR

RRx

R Rx

1

52

12

1

2

=

++

x

to lower logic threshold.

0.01 F

ENCODE

SOURCE

ENCODE

AD10265

Rx

V1

5V

R1

R2

Figure 7. Lower Threshold for Encode

V

R

RRx

1

52

2

1

=

+

to raise logic threshold.

0.01 F

ENCODE

SOURCE

ENCODE

AD10265

Rx

V1

5V

R1

R2

AVCC

Figure 8. Raise Logic Threshold for Encode

While the single-ended encode will work well for many applica-

tions, driving the encode differentially will provide increased

performance. Depending on circuit layout and system noise,

a 1 dB to 3 dB improvement in SNR can be realized. It is

recommended that differential TTL logic be used, however,

because most TTL families that support complementary outputs

are not delay or slew rate matched. Instead, it is recommended

that the encode signal be ac-coupled into the ENCODE and

ENCODE pins.

The simplest option is shown below. The low jitter TTL signal is

coupled with a limiting resistor, typically 100

, to the primary

side of an RF transformer (these transformers are inexpensive

and readily available; part number in Figure 9 is from Mini-

Circuits). The secondary side is connected to the ENCODE

and

ENCODE pins of the converter. Since both encode inputs

are self-biased, no additional components are required.

TTL

ENCODE

AD10265

100

T1–1T

Figure 9. TTL Source—Differential Encode

A clean sine wave may be substituted for a TTL clock. In this

case, the matching network is shown below. Select a transformer

ratio to match source and load impedances. The input impedance

of the AD10265 encode is approximately 11 k

differentially.

Therefore “R,” shown in Figure 10, may be any value that is

convenient for available drive power.

ENCODE

AD10265

R

T1–1T

SINE

SOURCE

Figure 10. Sine Source—Differential Encode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962R0153702QXX | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

| 5962G0153702QXC | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

| 5962H0153702VXC | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

| 5962H0153702VXX | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

| 5962F0153702VXA | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-9866101QXA | 制造商:Texas Instruments 功能描述:5962-9866101QXA,C6X DSP,840 MFLOPS,CBGA - Rail/Tube 制造商:Texas Instruments 功能描述:SMV320C6701GLPW14 CLASS V DSP 840MFLOPS |

| 5962-9866101VXA | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Rad-Tolerant Class V Fltg Pt Dig Sig Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| 5962-9866102VXA | 制造商:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| 59629873401CA | 制造商:Texas Instruments 功能描述:54ACTQ04DMBQ |

| 5962-98A1601VXA WAF | 制造商:Honeywell Sensing and Control 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。