- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67347 > 5962-9865901HXA (ANALOG DEVICES INC) DUAL 3-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 PDF資料下載

參數(shù)資料

| 型號(hào): | 5962-9865901HXA |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | DUAL 3-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 封裝: | CERAMIC, LCC-68 |

| 文件頁(yè)數(shù): | 18/24頁(yè) |

| 文件大小: | 2403K |

| 代理商: | 5962-9865901HXA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

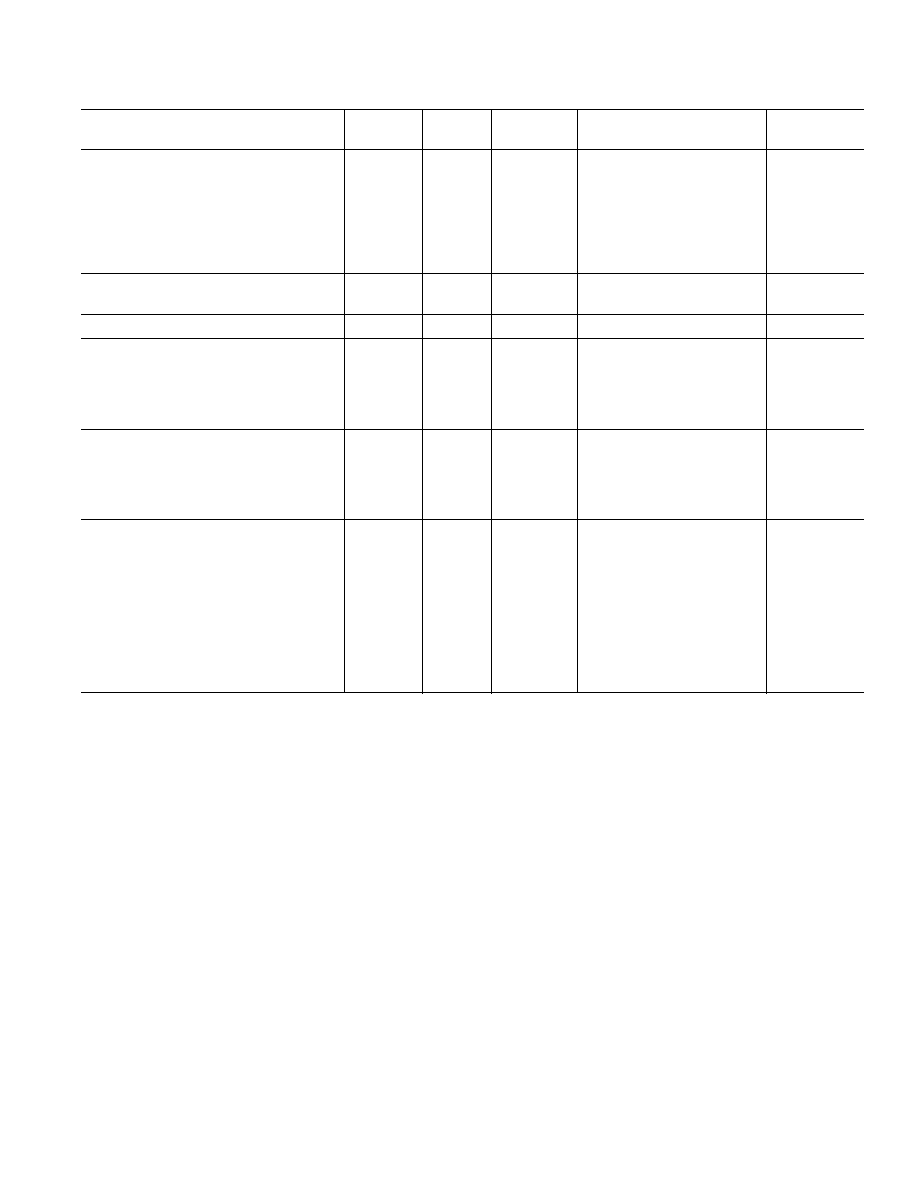

Test

Mil

AD10265AZ

Parameter

Temp

Level

Subgroup

Min

Typ

Max

Unit

SPURIOUS-FREE DYNAMIC RANGE

9

Analog Input @ 1.24 MHz

25

°C

I

4

75

80

dBFS

Full

II

5, 6

74

80

dBFS

@ 17 MHz

25

°C

I

4

71

80

dBFS

Full

II

5, 6

70

79

dBFS

@ 32 MHz

25

°C

V

79

dBFS

Full

V

79

dBFS

TWO-TONE IMD REJECTION

10

f1, f2 @ –7 dBFS

Full

V

4, 5, 6

66

77

dBc

CHANNEL-TO-CHANNEL ISOLATION

11

25

°CIV

12

80

dB

LINEARITY

Differential Nonlinearity

(Encode = 20 MHz)

25

°C

IV

12

–1.0

±0.5

+1.5

LSB

Integral Nonlinearity

(Encode = 20 MHz)

Full

V

±1.25

LSB

DIGITAL OUTPUTS

Logic Compatibility

CMOS

Logic “1” Voltage

Full

I

1, 2, 3

2.8

DVCC – 0.2

V

Logic “0” Voltage

Full

I

1, 2, 3

0.2

0.5

V

Output Coding

Two’s Complement

POWER SUPPLY

AVCC Supply Voltage

Full

V

+5.0

V

I (AVCC) Current

Full

V

336

mA

AVEE Supply Voltage

Full

V

–5.0

V

I (AVEE) Current

Full

V

66

mA

DVCC Supply Voltage

Full

V

+3.3

V

I (DVCC) Current

Full

V

20

mA

ICC (Total) Supply Current

Full

I

1, 2, 3

422

520

mA

Power Dissipation (Total)

Full

I

1, 2, 3

2.1

2.4

W

Power Supply Rejection Ratio (PSRR)

Full

IV

12

0.01

0.02

% FSR/% VS

NOTES

1Gain tests are performed on A

IN1 over specified input voltage range.

2Input capacitance specifications show only ceramic package capacitance.

3Full power bandwidth is the frequency at which the spectral power of the fundamental frequency (as determined by FFT analysis) is reduced by 3 dB.

4ENCODE driven by single-ended source;

ENCODE bypassed to ground through 0.01

F capacitor.

5ENCODE may also be driven differentially in conjunction with

ENCODE; see “Encoding the AD10265” for details.

6Minimum and maximum conversion rates allow for variation in Encode Duty Cycle of 50%

± 5%.

7Analog Input signal power at –1 dBFS; signal-to-noise ratio (SNR) is the ratio of signal level to total noise (first 5 harmonics removed). Encode = 65 MSPS.

8Analog Input signal power at –1 dBFS; signal-to-noise and distortion (SINAD) is the ratio of signal level to total noise + harmonics. Encode = 65 MSPS.

9Analog Input signal equal –1 dBFS; SFDR is ratio of converter full scale to worst spur.

10Both input tones at –7 dBFS; two-tone intermodulation distortion (IMD) rejection is the ratio of either tone to the worst third order intermod product. f1 = 17.0 MHz

± 100 kHz, f2 = 18.0 MHz ± 100 kHz.

11Channel-to-channel isolation tested with A channel/50 ohm terminated <A

IN2 grounded, and a full-scale signal applied to B channel (A IN1).

All specifications guaranteed within 100 ms of initial power-up, regardless of sequencing.

Specifications subject to change without notice.

AD10265

–3–

REV. A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962R0153702QXX | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

| 5962G0153702QXC | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

| 5962H0153702VXC | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

| 5962H0153702VXX | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

| 5962F0153702VXA | QUAD 2-CHANNEL, CROSS POINT SWITCH, DFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-9866101QXA | 制造商:Texas Instruments 功能描述:5962-9866101QXA,C6X DSP,840 MFLOPS,CBGA - Rail/Tube 制造商:Texas Instruments 功能描述:SMV320C6701GLPW14 CLASS V DSP 840MFLOPS |

| 5962-9866101VXA | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Rad-Tolerant Class V Fltg Pt Dig Sig Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| 5962-9866102VXA | 制造商:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| 59629873401CA | 制造商:Texas Instruments 功能描述:54ACTQ04DMBQ |

| 5962-98A1601VXA WAF | 制造商:Honeywell Sensing and Control 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。