- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F400B3 (Intel Corp.) SMART 3 ADVANCED BOOT BLOCK WORD-WIDE PDF資料下載

參數(shù)資料

| 型號: | 28F400B3 |

| 廠商: | Intel Corp. |

| 英文描述: | SMART 3 ADVANCED BOOT BLOCK WORD-WIDE |

| 中文描述: | 智能3高級啟動塊字寬 |

| 文件頁數(shù): | 5/49頁 |

| 文件大?。?/td> | 427K |

| 代理商: | 28F400B3 |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

E

1.0

SMART 3 ADVANCED BOOT BLOCK

–WORD-WIDE

5

PRELIMINARY

INTRODUCTION

This

specifications for the Advanced Boot Block flash

memory family, which is optimized for low power,

portable systems. This family of products features

1.8V

–2.2V or 2.7V–3.6V I/Os and a low V

CC

/V

PP

operating range of 2.7V–3.6V for read and

program/erase operations. In addition this family is

capable of fast programming at 12V. Throughout

this document, the term “2.7V” refers to the full

voltage range 2.7V–3.6V (except where noted

otherwise) and “V

PP

= 12V” refers to 12V ±5%.

Section 1 and 2 provides an overview of the flash

memory family including applications, pinouts and

pin descriptions. Section 3 describes the memory

organization and operation for these products.

Finally, Sections 4, 5, 6 and 7 contain the

operating specifications.

preliminary

datasheet

contains

the

1.1

Smart 3 Advanced Boot Block

Flash Memory Enhancements

The new 4-Mbit, 8-Mbit, and 16-Mbit Smart 3

Advanced Boot Block flash memory provides a

convenient upgrade from and/or compatibility to

previous 4-Mbit and 8-Mbit Boot Block products.

The Smart 3 product functions are similar to lower

density products in both command sets and

operation, providing similar pinouts to ease density

upgrades.

The Smart 3 Advanced Boot Block flash memory

features

Enhanced blocking for easy segmentation of

code and data or additional design flexibility

Program Suspend command which permits

program suspend to read

WP# pin to lock and unlock the upper two (or

lower two, depending on location) 4-Kword

blocks

V

CCQ

input for 1.8V–2.2V on all I/Os. See

Figure 1-4 for pinout diagrams and V

CCQ

location

Maximum program time specification for

improved data storage.

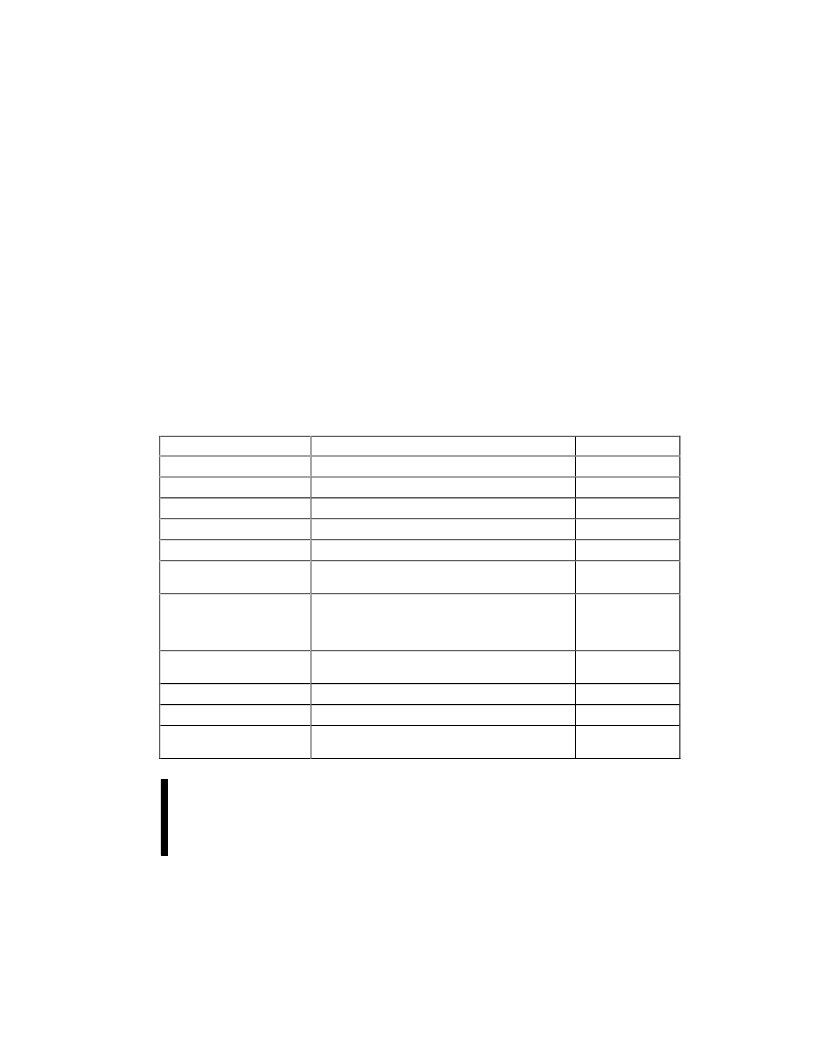

Table 1. Smart 3 Advanced Boot Block Feature Summary

Feature

28F160B3

Reference

V

CC

Read Voltage

2.7V– 3.6V

Table 9, Table 12

V

CCQ

I/O Voltage

1.8V–2.2V or 2.7V– 3.6V

Table 9, Table 12

V

PP

Program/Erase Voltage

2.7V– 3.6V or 11.4V– 12.6V

Table 9, Table 12

Bus Width

16 bit

Table 2

Speed

120 ns

Table 15

Memory Arrangement

256-Kbit x 16 (4-Mbit), 512-Kbit x 16 (8-Mbit),

1024-Kbit x 16 (16-Mbit)

Blocking (top or bottom)

Eight 4-Kword parameter blocks (4/8/16) &

Seven 32-Kword blocks (4-Mbit)

Fifteen 32-Kword blocks (8-Mbit)

Thirty-one 32-Kword main blocks (16-Mbit)

Section 2.2

Figures 5 and 6

Locking

WP# locks/unlocks parameter blocks

All other blocks protected using V

PP

switch

Section 3.3

Table 8

Operating Temperature

Extended: –40

°

C to +85

°

C

Table 9, Table 12

Program/Erase Cycling

10,000 cycles

Table 9, Table 12

Packages

48-Lead TSOP, 48-Ball

μ

BGA* CSP

Figures 1, 2, 3,

and 4

相關PDF資料 |

PDF描述 |

|---|---|

| 28F400BL-TB | 4-MBlT (256K x 16, 512K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F400BV-TB | 4-MBIT (256K X 16, 512K X 8)SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 28F400BX-TB | 4-MBIT (256K X 16, 512K X 8) BOOT BLOCK FLASH MEMORY FAMILY |

| 28F410-100M1 | 4M-BIT (512K X 8) CMOS FLASH MEMORY |

| 28F512 | 512K(64Kx8)CMOS FLASH MEMORY |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 28F400B5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SMART 5 BOOT BLOCK. FLASH MEMORY FAMILY 2. 4. 8 MBIT |

| 28F400B5WG8BET | 制造商: 功能描述: 制造商:Micron Technology Inc 功能描述: 制造商:undefined 功能描述: |

| 28F400BL-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-MBlT (256K x 16. 512K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F400BL-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-MBlT (256K x 16. 512K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F400BL-TB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:4-MBlT (256K x 16, 512K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

發(fā)布緊急采購,3分鐘左右您將得到回復。