- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371367 > 21054E (Microchip Technology Inc.) The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each PDF資料下載

參數(shù)資料

| 型號(hào): | 21054E |

| 廠商: | Microchip Technology Inc. |

| 元件分類: | EEPROM |

| 英文描述: | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 中文描述: | 該CAT24FC02是一個(gè)2 KB的EEPROM的國內(nèi)256個(gè)8位每字舉辦的串行CMOS |

| 文件頁數(shù): | 6/12頁 |

| 文件大小: | 76K |

| 代理商: | 21054E |

24AA16

DS21054E-page 6

1996 Microchip Technology Inc.

5.0

ACKNOWLEDGE POLLING

Since the device will not acknowledge during a write

cycle, this can be used to determine when the cycle is

complete (this feature can be used to maximize bus

throughput). Once the stop condition for a write com-

mand has been issued from the master, the device ini-

tiates the internally timed write cycle. ACK polling can

be initiated immediately. This involves the master send-

ing a start condition followed by the control byte for a

write command (R/W = 0). If the device is still busy with

the write cycle, then no ACK will be returned. If the

cycle is complete, then the device will return the ACK

and the master can then proceed with the next read or

write command. See Figure 5-1 for flow diagram.

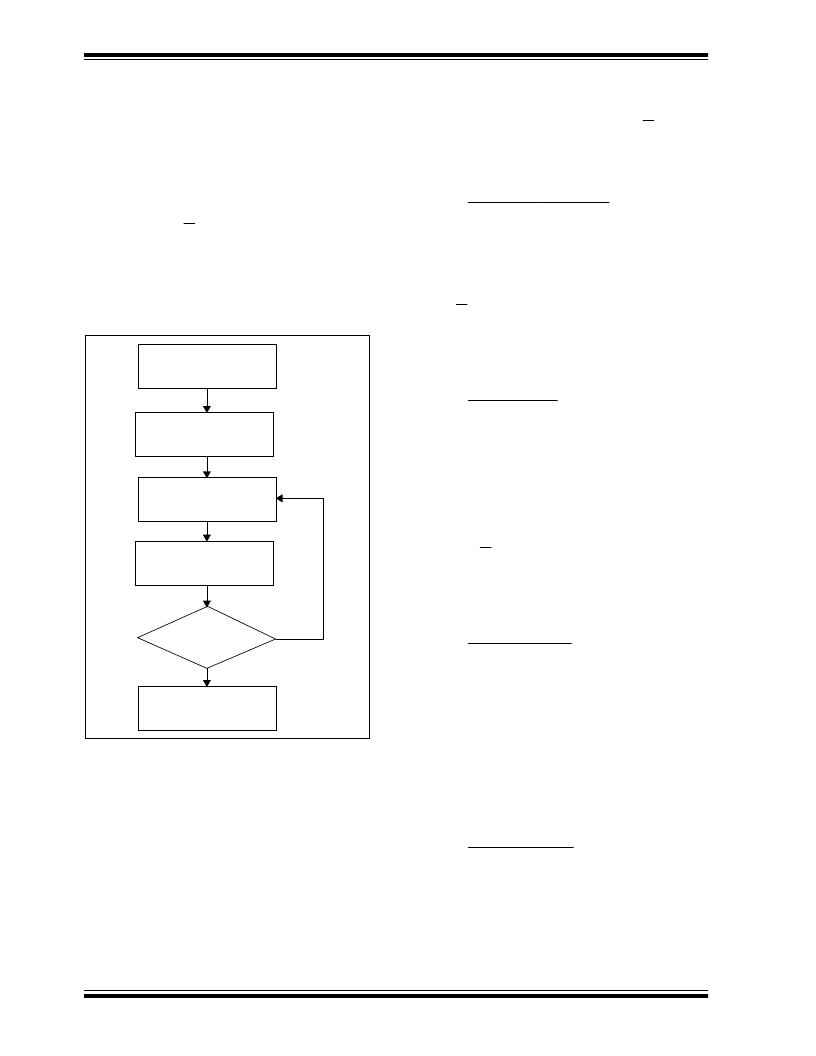

FIGURE 5-1:

ACKNOWLEDGE POLLING

FLOW

6.0

WRITE PROTECTION

The 24AA16 can be used as a serial ROM when the

WP pin is connected to V

CC

. Programming will be inhib-

ited and the entire memory will be write-protected.

Send

Write Command

Send Stop

Condition to

Initiate Write Cycle

Send Start

Send Control Byte

with R/W = 0

Did Device

Acknowledge

(ACK = 0)

Next

Operation

NO

YES

7.0

READ OPERATION

Read operations are initiated in the same way as write

operations with the exception that the R/W bit of the

slave address is set to one. There are three basic types

of read operations: current address read, random read,

and sequential read.

7.1

Current Address Read

The 24AA16 contains an address counter that main-

tains the address of the last word accessed, internally

incremented by one. Therefore, if the previous access

(either a read or write operation) was to address n, the

next current address read operation would access data

from address n + 1. Upon receipt of the slave address

with R/W bit set to one, the 24AA16 issues an acknowl-

edge and transmits the 8-bit data word. The master will

not acknowledge the transfer but does generate a stop

condition and the 24AA16 discontinues transmission

(Figure 7-1).

7.2

Random Read

Random read operations allow the master to access

any memory location in a random manner. To perform

this type of read operation, first the word address must

be set. This is done by sending the word address to the

24AA16 as part of a write operation. After the word

address is sent, the master generates a start condition

following the acknowledge. This terminates the write

operation, but not before the internal address pointer is

set. Then the master issues the control byte again but

with the R/W bit set to a one. The 24AA16 will then

issue an acknowledge and transmits the eight bit data

word. The master will not acknowledge the transfer but

does generate a stop condition and the 24AA16 discon-

tinues transmission (Figure 7-2).

7.3

Sequential Read

Sequential reads are initiated in the same way as a ran-

dom read except that after the 24AA16 transmits the

first data byte, the master issues an acknowledge as

opposed to a stop condition in a random read. This

directs the 24AA16 to transmit the next sequentially

addressed 8-bit word (Figure 7-3).

To provide sequential reads the 24AA16 contains an

internal address pointer which is incremented by one at

the completion of each operation. This address pointer

allows the entire memory contents to be serially read

during one operation.

7.4

Noise Protection

The 24AA16 employs a V

CC

threshold detector circuit

which disables the internal erase/write logic if the V

CC

is below 1.5 volts at nominal conditions.

The SCL and SDA inputs have Schmitt trigger and filter

circuits which suppress noise spikes to assure proper

device operation even on a noisy bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 21084 | AMD-K6 Processor Bios Design Application Note AMD-K6 Processor I/O Model Application Note |

| 21085 | AMD-K6 Processor I/O Model Application Note AMD-K6 Processor Thermal Solution Design Application Note |

| 21086 | SYSCALL and SYSRET Instruction Specification? 341KB (PDF) |

| 2108I | ALARMMODUL |

| 210A200 | Synchro/Resolver Reference Oscillator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 21055-4 | 制造商:TE Connectivity 功能描述: 制造商:TE Connectivity 功能描述:WASHER,FLAT,REGULAR SERIES - Bulk 制造商:TE CONNECTIVITY 功能描述: |

| 21055-48 | 制造商:American Power Conversion Corp (APC by Schneider Electric) 功能描述:PATCH PANEL, CAT 5 ENHANCED, 48 PORT, RJ45 TO 110, 568 A AND B COLOR CODED, 45 DEGREE ANGLED RJ45 |

| 21055-5 | 制造商:TE Connectivity 功能描述:WASHER,FLAT,REGULAR SERIES |

| 2105-555-REV-B | 制造商:MOLEX 功能描述: |

| 21055-6 | 制造商:TE Connectivity 功能描述: 制造商:TE Connectivity 功能描述:WASHER,FLAT,REGULAR SERIES - Bulk 制造商:TE CONNECTIVITY 功能描述:WASHER,FLAT,REGULAR SERIES |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。