- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293745 > 1894-40KLFT (INTEGRATED DEVICE TECHNOLOGY INC) DATACOM, INTERFACE CIRCUIT, QCC40 PDF資料下載

參數(shù)資料

| 型號(hào): | 1894-40KLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 網(wǎng)絡(luò)接口 |

| 英文描述: | DATACOM, INTERFACE CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, ROHS COMPLIANT, QFN-40 |

| 文件頁數(shù): | 34/52頁 |

| 文件大?。?/td> | 459K |

| 代理商: | 1894-40KLFT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE

PHYCEIVER

IDT / ICS 10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 4

ICS1894-40

REV C 092909

Notes:

1. Ipd = Input with internal pull-down.

Ipu = Input with internal pull-up.

Opu = Output with internal pull-up.

Ipu/O = Input with internal pull-up during power-up/reset; output pin otherwise.

Ipd/O = Input with internal pull-down during power-up/reset; output pin otherwise.

2. MII Rx Mode: The RXD[3..0] bits are synchronous with RXCLK. When RXDV is asserted, RXD[3..0] presents

valid data to MAC through the MII. RXD[3..0] is invalid when RXDV is de-asserted.

3. RMII Rx Mode: The RXD[1:0] bits are synchronous with REF_CLK. For each clock period in which CRS_DV is

asserted, two bits of recovered data are sent from the PHY.

4. MII Tx Mode: The TXD[3..0] bits are synchronous with TXCLK. When TXEN is asserted, TXD[3..0] presents valid

data from the MAC through the MII. TXD[3..0] has no effect when TXEN is de-asserted.

5. RMII Tx Mode: The TXD[1:0] bits are synchronous with REF_CLK. For each clock period in which TX_EN is

asserted, two bits of data are received by the PHY from the MAC.

28

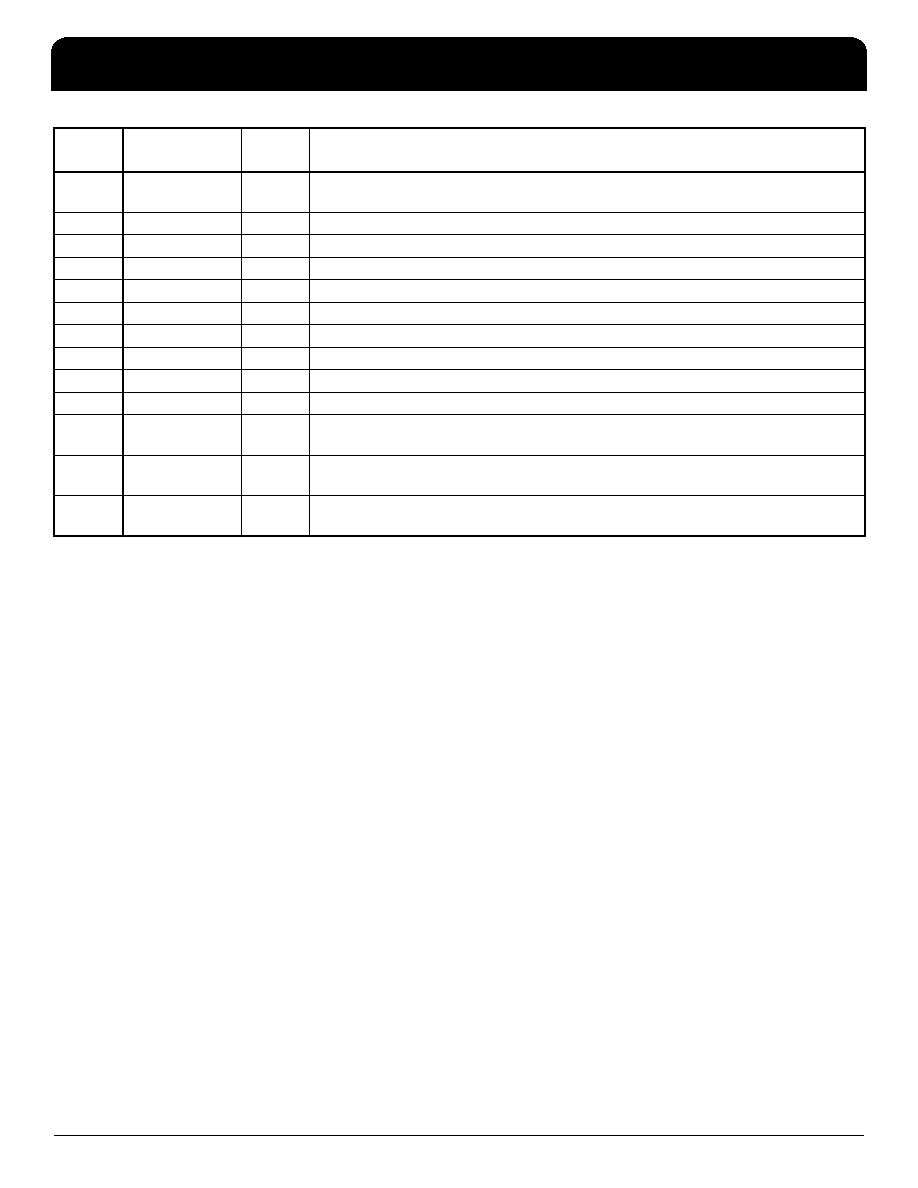

SPEED/

TXCLK

IO/Ipu

10M/100M select as input (during power on reset and hardware reset)

Transmit clock for MII as output

29

TXEN

Input

Transmit enable for both RMII and MII

30

TXD0

Input

Transmit data Bit 0 for both RMII and MII

31

VDDD

Power

Core Power Supply

32

LED3

IO/Ipd

LED3 output

33

TXD1

Input

Transmit data Bit 1for both RMII and MII

34

TXT2

Input

Transmit data Bit 2 for MII

35

TXD3

Input

Transmit data Bit 3 for MII

36

REF_OUT

Output

25 MHz crystal output

37

REF_IN

Input

25 MHz crystal (or clock) input for MII. 50MHz clock input for RMII

38

P4/LED2

IO/Ipu

PHY address Bit 4 as input (during power on reset and hardware reset)

And LED # 2 as output

39

P0/LED0

IO

PHY address Bit 0 as input (during power on reset and hardware reset) and LED #

0(function configurable, default is "activity/no activity") as output

40

P1/LED1

IO

PHY address Bit 1 as input (during power on reset and hardware reset) and LED #

1 (function configurable, default is "10/100 mode") as output

Pin

Number

Pin

Name

Pin

Type

Pin Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 1895230000 | 15 A, STRIP TERMINAL BLOCK, 2 ROWS, 2 DECKS |

| 18F-08P-241 | 8 CONTACT(S), CABLE MOUNT, MINI DIN CONNECTOR, PLUG |

| 18F-08P-244 | 8 CONTACT(S), CABLE MOUNT, MINI DIN CONNECTOR, PLUG |

| 18F-08S-011 | 8 CONTACT(S), BOARD AND CABLE MOUNT, MINI DIN CONNECTOR, SOCKET |

| 18F-08S-014 | 8 CONTACT(S), BOARD AND CABLE MOUNT, MINI DIN CONNECTOR, SOCKET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 1894410000 | 制造商:Weidmuller 功能描述:CONN TERM BLOCKS SKT 4 POS 5.08MM SCRW ST PNL MNT 10A - Bulk |

| 1894419 | 功能描述:可插拔接線端子 MSTBA 2.5/ 5-G- 5,08 BK AU RoHS:否 制造商:Phoenix Contact 產(chǎn)品:Plugs 系列:PTS 端接類型:Spring Cage 位置/觸點(diǎn)數(shù)量:5 線規(guī)量程:26-14 節(jié)距:5 mm 電流額定值:10 A 電壓額定值:250 V 安裝風(fēng)格: 安裝角: 觸點(diǎn)電鍍: |

| 1894420000 | 制造商:Weidmuller 功能描述:CONN TERM BLOCKS SKT 5 POS 5.08MM SCRW ST PNL MNT 10A - Bulk |

| 1894430000 | 制造商:Weidmuller 功能描述:CONN TERM BLOCKS SKT 6 POS 5.08MM SCRW ST PNL MNT 10A - Bulk |

| 1894440000 | 功能描述:BLZ 5.08/07/270F SN OR BX 制造商:weidmuller 系列:* 零件狀態(tài):有效 標(biāo)準(zhǔn)包裝:36 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。