- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293745 > 1894-40KLF (INTEGRATED DEVICE TECHNOLOGY INC) DATACOM, INTERFACE CIRCUIT, QCC40 PDF資料下載

參數(shù)資料

| 型號(hào): | 1894-40KLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 網(wǎng)絡(luò)接口 |

| 英文描述: | DATACOM, INTERFACE CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, ROHS COMPLIANT, QFN-40 |

| 文件頁(yè)數(shù): | 23/52頁(yè) |

| 文件大?。?/td> | 459K |

| 代理商: | 1894-40KLF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE

PHYCEIVER

IDT / ICS 10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 3

ICS1894-40

REV C 092909

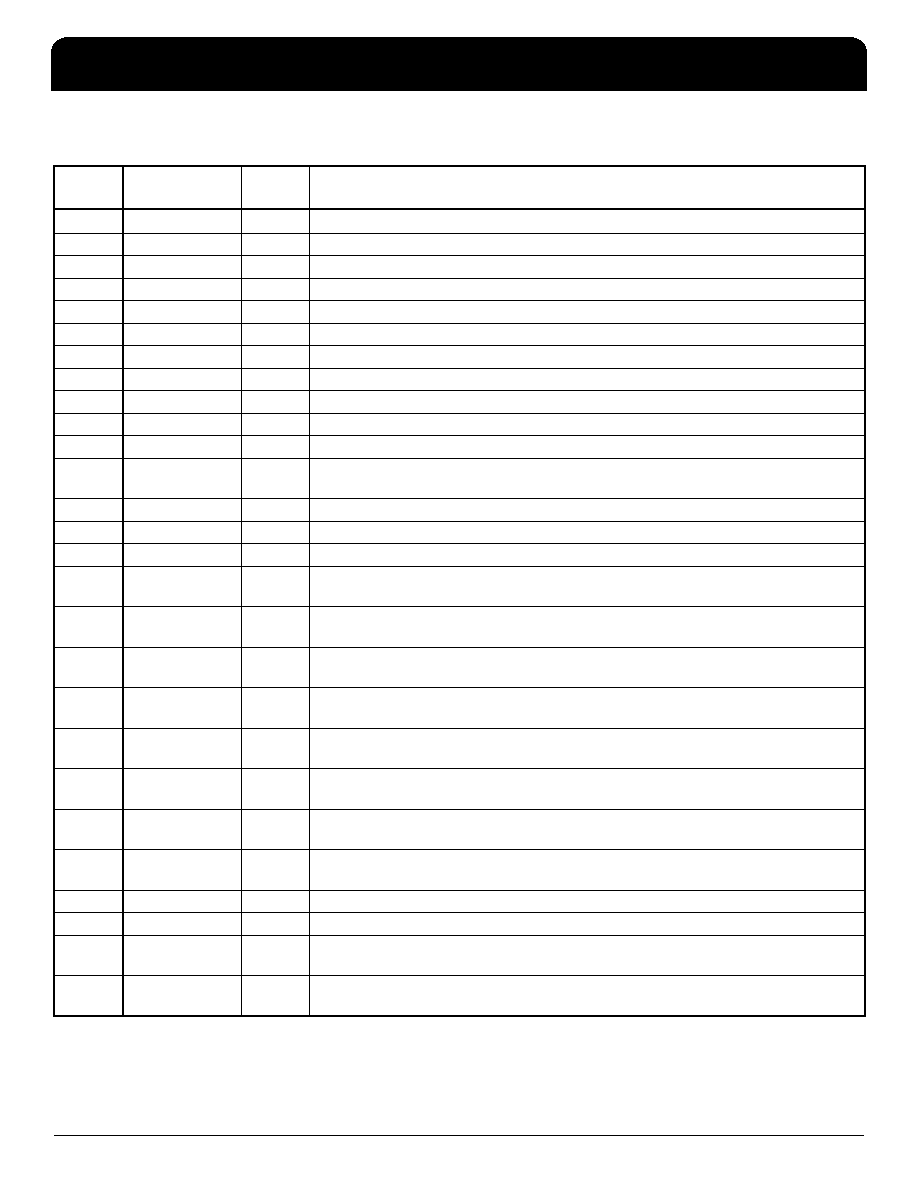

Pin Descriptions

Pin

Number

Pin

Name

Pin

Type

Pin Description

1

AMDIX

IN/Ipu

AMDIX Enable

2

TP_AP

AIO

Twisted pair port A (for either transmit or receive) positive signal

3

TP_AN

AIO

Twisted pair port A (for either transmit or receive) negative signal

4

VSS

Ground Connect to ground.

5

VDD

Power

3.3V Power Supply

6

TP_BN

AIO

Twisted pair port B (for either transmit or receive) negative signal

7

TP_BP

AIO

Twisted pair port B (for either transmit or receive) positive signal

8

VDD

Power

3.3V Power Supply

9

TCSR

AIO

Transmit Current bias pin, connected to Vdd and ground via two resistors.

10

VSS

Ground Connect to ground.

11

RESET_N

Input

Hardware reset for the whole chip (active low)

12

P2/INT

IO/Ipd

PHY address Bit 2 as input (during power on reset and hardware reset)

Interrupt output as output (default active low, can be programmed to active high)

13

MDIO

IO

Management Data Input/Output

14

MDC

Input

Management Data Clock

15

VDDIO

Power

3.3 V IO Power Supply.

16

HWSW/

CRS

IO/Ipu

Hard pin select enable as input (during power on reset and hardware reset) and

MII CRS as output

17

Regpin/

COL

IO/Ipd

Full register access enable as input (during power on reset and hardware reset) and

MII COL output

18

AMDIX/RXD3

IO/Ipu

AMDIX enable as input (during power on reset and hardware reset)

Receive data Bit 3 for MII

19

P3/RXD2

IO/Ipd

PHY address Bit 3 as input (during power on reset and hardware reset)

Receive data Bit 2 for MII as output.

20

RXTRI/

RXD1

IO/Ipu

RX isolate enable (during power on reset and hardware reset)

Received data Bit 1 for both RMII and MII

21

SI/LED4

IO/Ipd

MII/SI mode select as input (during power on reset and hardware reset) and

LED # 4 as output

22

FDPX/

RXD0

IO/Ipu

Full duplex enable (during power on reset and hardware reset)

Received data Bit 0 for both RMII and MII

23

RMII/RXDV

IO/Ipd

RMII/MII select as input (during power on reset and hardware reset)

Receive data valid for MII and CRS_DV for RMII as output

24

SPEED

Ipd

10/100M input select. 1 = 100M mode, 0 = 10M mode.

25

TXER

IN

TXER Input

26

ANSEL/

RXCLK9

IO/Ipu

Auto-negotiation enable(during power on reset and hardware reset)

Receive clock MII

27

NOD/

RXER

IO/Ipd

Node/repeater select (during power on reset and hardware reset)

Receive error

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 1894-40KLFT | DATACOM, INTERFACE CIRCUIT, QCC40 |

| 1895230000 | 15 A, STRIP TERMINAL BLOCK, 2 ROWS, 2 DECKS |

| 18F-08P-241 | 8 CONTACT(S), CABLE MOUNT, MINI DIN CONNECTOR, PLUG |

| 18F-08P-244 | 8 CONTACT(S), CABLE MOUNT, MINI DIN CONNECTOR, PLUG |

| 18F-08S-011 | 8 CONTACT(S), BOARD AND CABLE MOUNT, MINI DIN CONNECTOR, SOCKET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 1894-40KLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE |

| 1894410000 | 制造商:Weidmuller 功能描述:CONN TERM BLOCKS SKT 4 POS 5.08MM SCRW ST PNL MNT 10A - Bulk |

| 1894419 | 功能描述:可插拔接線端子 MSTBA 2.5/ 5-G- 5,08 BK AU RoHS:否 制造商:Phoenix Contact 產(chǎn)品:Plugs 系列:PTS 端接類型:Spring Cage 位置/觸點(diǎn)數(shù)量:5 線規(guī)量程:26-14 節(jié)距:5 mm 電流額定值:10 A 電壓額定值:250 V 安裝風(fēng)格: 安裝角: 觸點(diǎn)電鍍: |

| 1894420000 | 制造商:Weidmuller 功能描述:CONN TERM BLOCKS SKT 5 POS 5.08MM SCRW ST PNL MNT 10A - Bulk |

| 1894430000 | 制造商:Weidmuller 功能描述:CONN TERM BLOCKS SKT 6 POS 5.08MM SCRW ST PNL MNT 10A - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。