- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄24691 > 05F8031 IC-SM-QUAD 12 BIT DAC PDF資料下載

參數(shù)資料

| 型號(hào): | 05F8031 |

| 英文描述: | IC-SM-QUAD 12 BIT DAC |

| 中文描述: | 集成電路釤四路12位DAC |

| 文件頁(yè)數(shù): | 5/12頁(yè) |

| 文件大小: | 502K |

| 代理商: | 05F8031 |

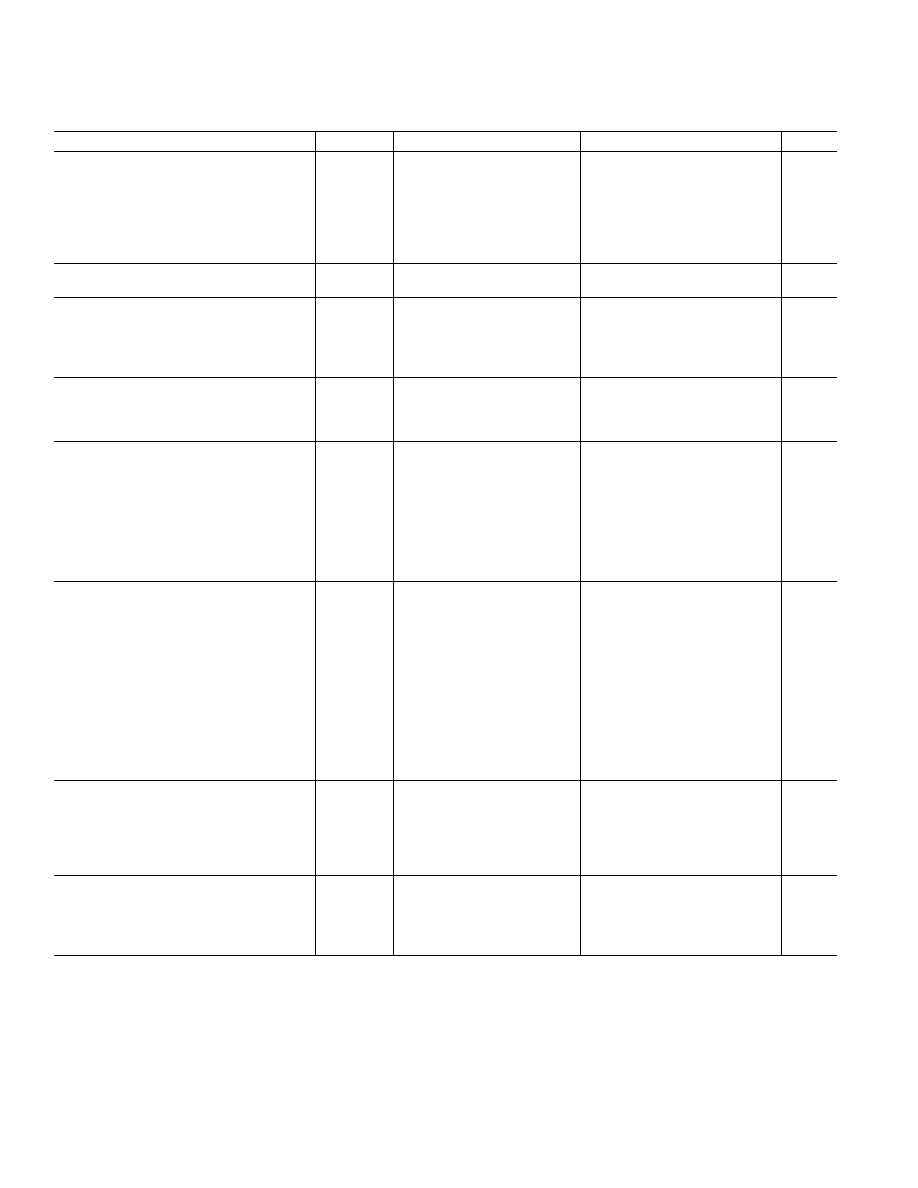

DAC8412/DAC8413–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

Parameter

Symbol

Conditions

Min

Typ

Max

Units

Integral Linearity “E”

INL

0.25

±0.5

LSB

Integral Linearity “F”

INL

±1

LSB

Differential Linearity

DNL

Monotonic Over Temperature

–1

LSB

Min Scale Error

VZSE

RL = 2 k± 2

LSB

Full-Scale Error

VFSE

RL = 2 k± 2

LSB

Min Scale Tempco

TCVZSE

RL = 2 k

15

ppm/

°C

Full-Scale Tempco

TCVFSE

RL = 2 k

20

ppm/

°C

MATCHING PERFORMANCE

Linearity Matching

±1

LSB

REFERENCE

Positive Reference Input Range

Note 2

VREFL + 2.5

VDD – 2 5

V

Negative Reference Input Range

Note 2

–10

VREFH – 2.5 V

Reference High Input Current

IREFH

–2.75

+1.5

+2.75

mA

Reference Low Input Current

IREFL

0

+2

+2.75

mA

AMPLIFIER CHARACTERISTICS

Output Current

IOUT

–5

+5

mA

Settling Time

tS

to 0.01%

6

s

Slew Rate

SR

10% to 90%

2.2

V/

s

LOGIC CHARACTERISTICS

Logic Input High Voltage

VINH

TA = +25°C

2.4

V

Logic Input Low Voltage

VINL

TA = +25°C

0.8

V

Logic Output High Voltage

VOH

IOH = +0.4 mA

2.4

V

Logic Output Low Voltage

VOL

IOL = –1.6 mA

0.4

V

Logic Input Current

IIN

1

A

Input Capacitance

CIN

8pF

Crosstalk

>72

dB

Large Signal Bandwidth

–3 dB, VREFH = 0 to +10 V p-p

160

kHz

LOGIC TIMING CHARACTERISTICS

Note 3

WRITE

Chip Select Write Pulse Width

tWCS

80

40

ns

Write Setup

tWS

tWCS = 80 ns

0

ns

Write Hold

tWH

tWCS = 80 ns

0

ns

Address Setup

tAS

0ns

Address Hold

tAH

0ns

Load Setup

tLS

70

30

ns

Load Hold

tLH

30

10

ns

Write Data Setup

tWDS

tWCS = 80 ns

20

ns

Write Data Hold

tWDH

tWCS = 80 ns

0

ns

Load Pulse Width

tLWD

170

130

ns

Reset Pulse Width

tRESET

140

100

ns

READ

Chip Select Read Pulse Width

tRCS

130

100

ns

Read Data Hold

tRDH

tRCS = 130 ns

0

ns

Read Data Setup

tRDS

tRCS = 130 ns

0

ns

Data to Hi Z

tDZ

CL = 10 pF

150

ns

Chip Select to Data

tCSD

CL = 100 pF

120

160

ns

SUPPLY CHARACTERISTICS

Power Supply Sensitivity

PSS

14.25 V

≤ V

DD ≤ 15.75 V

150

ppm/V

Positive Supply Current

IDD

VREFH = +2.5 V

8.5

12

mA

Negative Supply Current

ISS

–10

–6.5

mA

Power Dissipation

PDISS

330

mW

NOTES

1All supplies can be varied

± 5%, and operation is guaranteed. Device is tested with nominal supplies.

2Operation is guaranteed over this reference range, but linearity is neither tested nor guaranteed.

3All input control signals are specified with tr = tf = 5 ns (10% to 90% of +5 V) and timed from a voltage level of 1.6 V.

Specifications subject to change without notice.

REV. C

–2–

(@ VDD = +15.0 V, VSS = –15.0 V, VLOGIC = +5.0 V, VREFH = +10.0 V, VREFL = –10.0 V,

–40 C

≤ T

A

≤ +85 C unless otherwise noted. See Note 1 for supply variations.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 934051200112 | 40 MHz - 750 MHz RF/MICROWAVE WIDE BAND HIGH POWER AMPLIFIER |

| 934051230112 | 40 MHz - 750 MHz RF/MICROWAVE WIDE BAND HIGH POWER AMPLIFIER |

| 934051510185 | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

| 934031080215 | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR, TO-236AB |

| 934051510115 | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 05FD101J03 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 05FD111J03 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 05FD161J03 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 05FD241J03 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 05FD271J03 | 制造商: 功能描述: 制造商:undefined 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。