- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372985 > ZPSD511B1-70UI Field-Programmable Peripheral PDF資料下載

參數(shù)資料

| 型號: | ZPSD511B1-70UI |

| 英文描述: | Field-Programmable Peripheral |

| 中文描述: | 現(xiàn)場可編程外圍 |

| 文件頁數(shù): | 81/153頁 |

| 文件大小: | 1036K |

| 代理商: | ZPSD511B1-70UI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁當(dāng)前第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

PSD5XX Famly

78

Counter/Timer

Operation

(Cont.)

9.6.1.8 Counter/Timer Clock Input

All Counter/Timers 0 through 3 have a common clock source. The Counter/Timers are

clocked from the output of a highly flexible and high resolution Divisor unit. The Divisor’s

input is the external Clock input pin. The Divisor DIV is a number in the range of

4

<

= DIV

<

= 280. Refer to Table 22 for exact values of DIV for different clock values.

Figure 42 details the PSD5XX Counter clock generation.

The Counter/Timer CLOCK input

(External Clock input)

(DIV)

=

where DIV = N

*

K and N = (4 + DLCY).

The value of K depends on the Scale-Bit (Bit 0 in the Global Command Register) in the

“Global Command Register” , K = 8 when Scale-Bit is set to 1 and K = 1 when Scale-Bit is

set to 0. DLCY is the number of Delay Cycles in the range of 0

<

= DLCY

<

= 31 set up in the

Delay Cycle Register. The fastest clock to service the Counter/Timer is = (Clock input / 4).

The maximum External Clock input value is 28 MHz and the fastest internal count frequency

is 7.0 MHz, i.e., a resolution of 143 ns. (Higher resolution can be achieved by using in

conjunction with GPLD macrocells). The default value of DIV is 4 (following a reset both K

and DLCY contain zeroes).

9.6.1.7 Termnal Counts (TCs)

The terminal counts (TC0 – TC3) generated by the Counter/Timers are made available

at Port E as outputs or as feedbacks to the ZPLD. Refer to Table 27a for pin assignments.

The terminal counts can be used to concatenate the 16-bit Counter/Timers into a

larger counter. Only the trailing edge of the TC signal can be used as input to another

Counter/Timer. For example, concatenating CTU0 and CTU1 requires the following

PPLD equation in the PSDabel file:

mc2tmr1 = tc0;

In order for a TC signal to come out, its respective bit in the Port E Special Function Out

Register must be set to 1. TC signals on Port E pins can be used as inputs to the ZPLD.

A TC signal goes high for the duration of at least four CLKIN periods whenever its

corresponding Timer Counting-Register overflows or underflows.

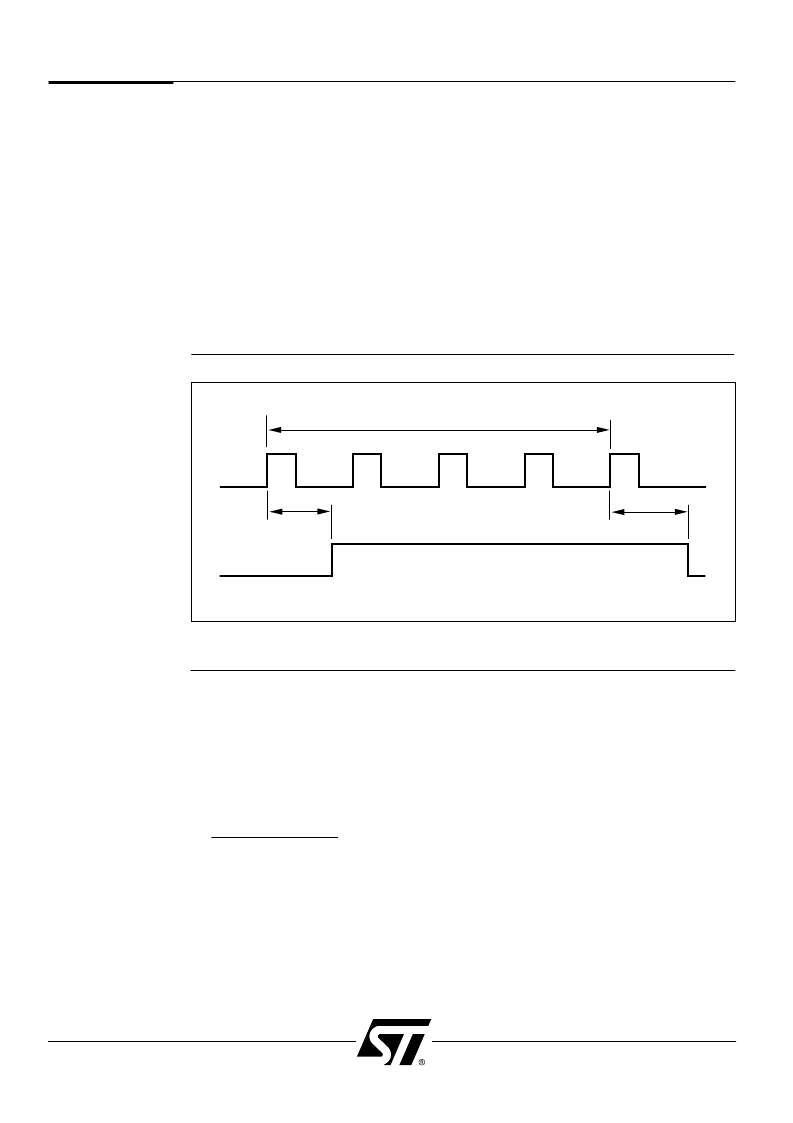

Figure 41 gives the timing relationship between CLKIN and the TC signal.

Figure 41. Timng Relationship Between CLKINand the TC Signal.

4 CLKIN PERIODS

CLKIN

TC - SIGNAL

30ns

30ns

NOTES:

1. Overflow occurs when a counter value changes from FFFFh to 0000h during incrementing.

2. Underflow occurs when a counter value changes from 0000h to FFFFh during decrementing.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZPSD511B1-90J | Field-Programmable Peripheral |

| ZPSD511B1-90JI | Field-Programmable Peripheral |

| ZPSD511B1-90LI | Field-Programmable Peripheral |

| ZPSD512B1-12UI | Field-Programmable Peripheral |

| ZPSD512B1-15J | Field-Programmable Peripheral |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZPSD512B1-C-90UI | 制造商:WSI 功能描述: |

| ZPSD513B1-C-15L | 制造商:WSI 功能描述: |

| ZPSD602E1-15L | 制造商:WSI 功能描述: |

| ZPSD611E1-15J | 制造商:WSI 功能描述: |

| ZPSD611E1-15JI | 制造商:WSI 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。