- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372985 > ZPSD511B1-12LI Field-Programmable Peripheral PDF資料下載

參數(shù)資料

| 型號(hào): | ZPSD511B1-12LI |

| 英文描述: | Field-Programmable Peripheral |

| 中文描述: | 現(xiàn)場(chǎng)可編程外圍 |

| 文件頁(yè)數(shù): | 91/153頁(yè) |

| 文件大?。?/td> | 1036K |

| 代理商: | ZPSD511B1-12LI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)當(dāng)前第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)

PSD5XX Famly

88

9.6.2.5 Software Load/Store Register:

Each bit in this register enables a load to the corresponding Counter/Timer from its

associated Image Register in Waveform, Pulse or WatchDog modes. The actual counts

are stored in their corresponding Image Register in event Counter or time capture modes.

Bit 6 of the Command Register must be set to “1” before writing to the software load/store

register.

Counter/Timer

(Cont.)

Software Load/Store 0 Bit:

If this bit is set to

1: Counter/Timer0 CNTR0 gets loaded from the Image

Register IMG0 or CNTR0 stores into IMG0 based on the

mode of operation

**

.

Software Load/Store 1 Bit:

If this bit is set to

1: Counter/Timer1 CNTR1 gets loaded from the Image

Register IMG1 or CNTR1 stores into IMG1 based on the

mode of operation

**

.

Software Load/Store 2 Bit:

If this bit is set to

1: Counter/Timer2 CNTR2 gets loaded from the Image

Register IMG2.

Software Load/Store 3 Bit:

If this bit is set to

1: Counter/Timer3 CNTR3 gets loaded from the Image

Register IMG3 or CNTR3 stores into IMG3 based on the

mode of operation

**

.

**

Load operation takes place in Waveform, Pulse and WatchDog mode.

Store operation takes place in Event Count and Time Capture mode.

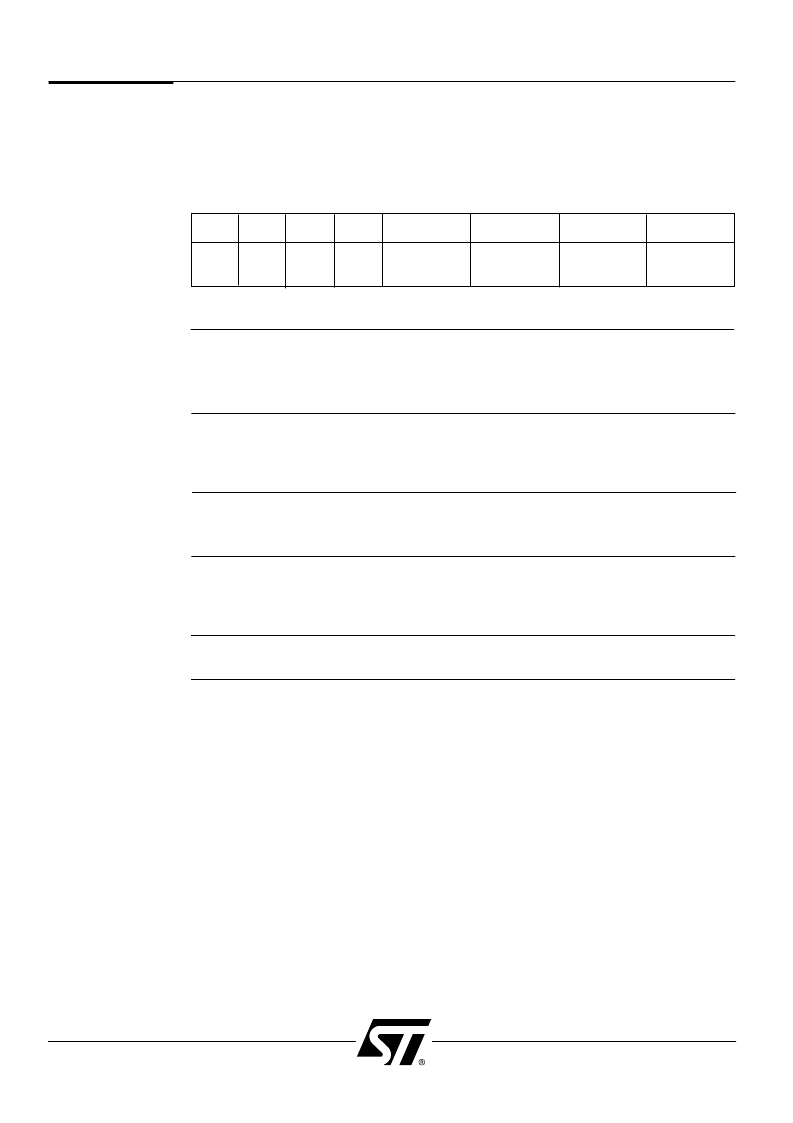

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

*

*

*

*

Software

Load/Store 3 Load/Store 2 Load/Store 1 Load/Store 0

Software

Software

Software

NOTE:

*

= Not used.

The Software load/store bits are automatically cleared by the served Counter.

In addition to four CTU registers, there are delay cycle and Counter/Timer status registers.

These are summarized on the following pages.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZPSD511B1-70JI | Field-Programmable Peripheral |

| ZPSD511B1-70LI | Field-Programmable Peripheral |

| ZPSD511B1-70LM | Schottky Barrier Diodes |

| ZPSD511B1-70U | Field-Programmable Peripheral |

| ZPSD511B1-70UI | Field-Programmable Peripheral |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZPSD512B1-C-90UI | 制造商:WSI 功能描述: |

| ZPSD513B1-C-15L | 制造商:WSI 功能描述: |

| ZPSD602E1-15L | 制造商:WSI 功能描述: |

| ZPSD611E1-15J | 制造商:WSI 功能描述: |

| ZPSD611E1-15JI | 制造商:WSI 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。