- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373785 > ZL50023 (Zarlink Semiconductor Inc.) Enhanced 4 K Digital Switch PDF資料下載

參數(shù)資料

| 型號(hào): | ZL50023 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Enhanced 4 K Digital Switch |

| 中文描述: | 增強(qiáng)為4 K數(shù)字開(kāi)關(guān) |

| 文件頁(yè)數(shù): | 32/80頁(yè) |

| 文件大小: | 1341K |

| 代理商: | ZL50023 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)

ZL50023

Data Sheet

32

Zarlink Semiconductor Inc.

Multiple connection memory locations can be programmed for BER tests such that the BER patterns can be

transmitted for multiple consecutive output channels. If consecutive input channels are not selected, the BER

receiver will not compare the bit patterns correctly. The number of output channels which the BER pattern occupies

has to be the same as the number of channels defined in the BER Length Register (BRLR) which defines how

many BER channels are to be monitored by the BER receiver.

For each input stream, there is a set of registers for the BER test. The registers are as follows:

BER Receiver Control Register (

BRCR

) - ST[n]CBER (bit 1) is used to clear the Bit Receiver Error Register

(BRER). ST[n]SBER (bit 0) is used to enable the per-stream BER receiver.

BER Receiver Start Register (

BRSR

) - ST[n]BRS7 - 0 (bit 7 - 0) defines the input channel from which the

BER sequence will start to be compared.

BER Receiver Length Register (

BRLR

) - ST[n]BL8 - 0 (bit 8 - 0) define how many channels the sequence

will last. Depending on the data rate being used, the BER test can last for a maximum of 32, 64, 128 or 256

channels at the data rates of 2.048, 4.096, 8.192 or 16.384 Mbps, respectively. The minimum length of the

BER test is a single channel. The user must take care to program the correct channel length for the BER test

so that the channel length does not exceed the total number of channels available in the stream.

BER Receiver Error Register (

BRER

) - This read-only register contains the number of counted errors. When

the error count reaches 0xFFFF, the BER counter will stop updating so that it will not overflow. ST[n]CBER

(bit 1) in the BER Receiver Control Register is used to reset the BRER register.

For normal BER operation, CMM (bit 0) must be 1 in the Connection Memory Low (CM_L). PCC1 - 0 (bits 2 - 1) in

the Connection Memory Low must be programmed to “10” to enable the per-stream based BER transmitters. For

each stream, the length (or total number of channels) of BER testing can be as long as one whole frame, but the

channels MUST be consecutive. Upon completion of programming the connection memory, the corresponding BER

receiver can be started by setting ST[n]SBER (bit 0) in the BRCR to high. There must be at least 2 frames (250

μ

s)

between completion of connection memory programming and starting the BER receiver before the BER receiver

can correctly identify BER errors. A 16-bit BER counter is used to count the number of bit errors.

16.0 PCM A-law/

μ

-law Translation

The ZL50023 provides per-channel code translation to be used to adapt pulse code modulation (PCM) voice or

data traffic between networks which use different encoding laws. Code translation is valid in both Connection Mode

and Message Mode.

In order to use this feature, the Connection Memory High (CM_H) entry for the output channel must be

programmed. V/D (bit 4) defines if the traffic in the channel is voice or data. Setting ICL1 - 0 (bits 3 - 2) programs the

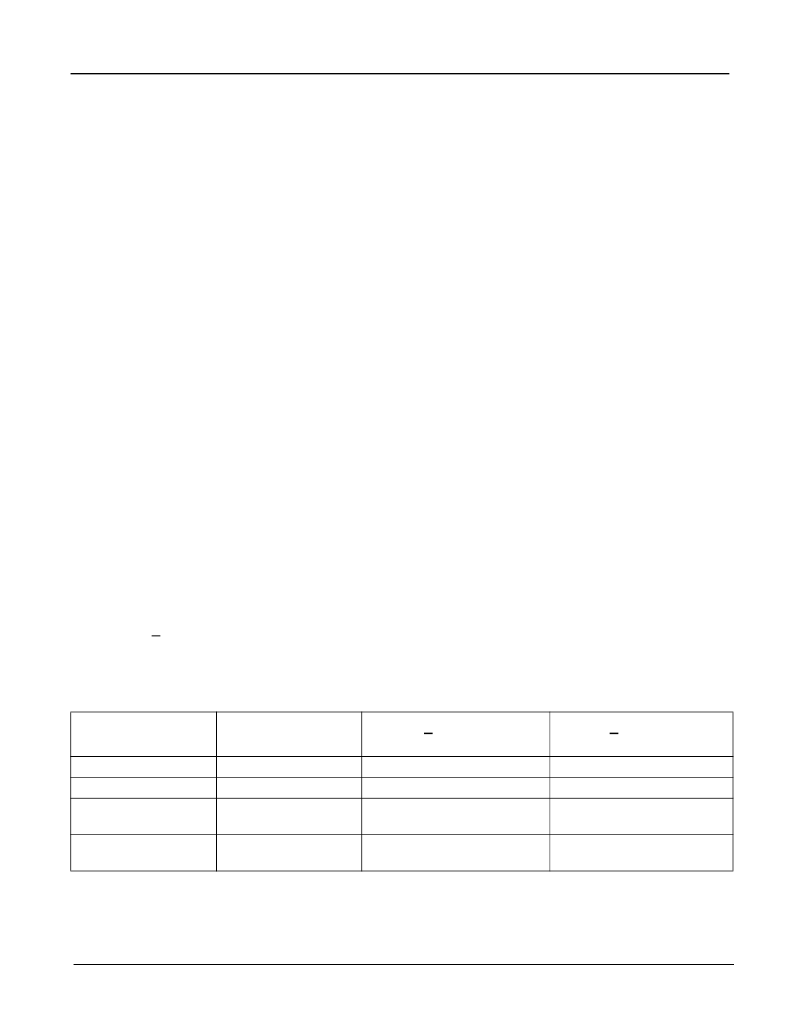

input coding law and OCL1 - 0 (bits 1- 0) programs the output coding law as shown in Table 10.

The different code options are:

For voice coding options, the ITU-T G.711 A-law and ITU-T G.711

μ

-law are the standard rules for encoding. A-law

without Alternate Bit Inversion (ABI) is an alternative code that does not invert the even bits (6, 4, 2, 0).

μ

-law

Input Coding

(ICL1- 0)

Output Coding

(OCL1 - 0)

Voice Coding

(V/D bit = 0)

Data Coding

(V/D bit = 1)

00

01

10

00

01

10

ITU-T G.711 A-law

ITU-T G.711

μ

-law

A-law without Alternate Bit

Inversion (ABI)

μ

-law without Magnitude

Inversion (MI)

No code

Alternate Bit Inversion (ABI)

Inverted Alternate Bit

Inversion (ABI)

All bits inverted

11

11

Table 10 - Input and Output Voice and Data Coding

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50023GAC | Enhanced 4 K Digital Switch |

| ZL50023QCC | Enhanced 4 K Digital Switch |

| ZL50030 | Flexible 4 K x 2 K Channel Digital Switch with H.110 Interface and 1 K x 1 K Local Switch |

| ZL50030GAC | Flexible 4 K x 2 K Channel Digital Switch with H.110 Interface and 1 K x 1 K Local Switch |

| ZL50031 | Flexible 4 K x 2 K Channel Digital Switch with H.110 Interface and 2 K x 2 K Local Switch |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50023_06 | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:Enhanced 4 K Digital Switch |

| ZL50023GAC | 制造商:Microsemi Corporation 功能描述: 制造商:Microsemi Corporation 功能描述:4K WITH RATE CONVERSION - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 4K-CH ENH 256PBGA 制造商:Microsemi Corporation 功能描述:IC TDM SWITCH 4K-CH ENH 256PBGA |

| ZL50023GAG2 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 4K X 4K 1.8V/3.3V 256BGA - Trays 制造商:Microsemi Corporation 功能描述:PB FREE PARALLEL ACCESS CIRCUIT (PAC) 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 4K-CH ENH 256PBGA 制造商:Microsemi Corporation 功能描述:IC TDM SWITCH 4K-CH ENH 256PBGA |

| ZL50023QCC | 制造商:Microsemi Corporation 功能描述: 制造商:Microsemi Corporation 功能描述:4K WITH RATE CONVERSION - Trays |

| ZL50023QCG1 | 制造商:Microsemi Corporation 功能描述:PB FREE 4K WITH RATE CONVERSION 制造商:Microsemi Corporation 功能描述:PB FREE 4K WITH RATE CONVERSION - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 4K-CH ENH 256LQFP 制造商:Microsemi Corporation 功能描述:IC TDM SWITCH 4K-CH ENH 256LQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。