- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373755 > Z16C30 (ZiLOG, Inc.) Integrated Universal Serial Controller(數(shù)據(jù)通信用集成通用串行控制器) PDF資料下載

參數(shù)資料

| 型號: | Z16C30 |

| 廠商: | ZiLOG, Inc. |

| 英文描述: | Integrated Universal Serial Controller(數(shù)據(jù)通信用集成通用串行控制器) |

| 中文描述: | 集成通用串行控制器(數(shù)據(jù)通信用集成通用串行控制器) |

| 文件頁數(shù): | 1/2頁 |

| 文件大小: | 62K |

| 代理商: | Z16C30 |

ZiLOG W

ELEPHONE

ORLDWIDE

: 408.558.8500 E

H

EADQUARTERS

MAIL

910 E. H

CSUPPORT

AMILTON

ZILOG

A

I

VENUE

NTERNET

AMPBELLHTTPWWWZILOGT

:

@

.

COM

.PRODUCT

B

LOCK

D

IAGRAM

F

Two independent, 0 to 10 mbps, full-duplex chan-

nels, each with two baud-rate generators (BRGS)

and one digital phase-locked loop (DPLL) for

clock recovery

32-Byte Data FIFO’s for each receiver and trans-

mitter

ASYNC mode with:

– 1–8 bits/character; 1/16 to two stop bits/charac-

ter in 1/16 bit increments

– Programmable clock factor

– Break detect and generation

– Odd, Even, Mark, Space, or no parity and fram-

ing error detection

Byte-oriented Synchronous mode with

– 1–8 bits/character

– 2- to 16-bit programmable SYNC character

– 16- or 32-Bit cyclic redundancy check (CRC)

and transmit-to-receive slaving (for X.21)

HDLC/SDLC mode with:

– 8-bit address compare

– Extended address field option

– 16- or 32-bit CRC

EATURES

– Programmable idle line condition

– Optional preamble transmission and loop mode

External character synchronous mode for receive

DMA interface with separate request and

acknowledge for each receiver and transmitter

G

ENERAL

D

ESCRIPTION

The Z16C30 USC Universal Serial Controller is a

dual-channel multi-protocol data communications

peripheral. Designed for use with any conventional

multiplexed or non-multiplexed bus, the USC

functions as a serial-to-parallel, parallel-to-serial

converter/controller, and may be software configured

to satisfy a wide variety of serial communications

applications. The device contains a variety of

sophisticated internal functions, including two baud

rate generators per channel, one digital phase-locked

loop per channel, character counters for both receive

and transmit in each channel, and 32-byte data

FIFO’s for each receiver and transmitter.

The CPU bus accesses have been shortened from 160

ns per access to 110 ns per access. The USC has a

transmit and receive clock range of up to 10 MHz (20

MHz when using the DPLL, BRG, or CTR to divide

the clock by 2 or more), and data transfer rates as

high as 10 Mbps (full duplex).

The

synchronous byte-oriented formats such as BISYNC,

and synchronous bit-oriented formats such as HDLC.

USC

handles

asynchronous

formats,

The device generates and checks CRC in any

synchronous mode and can be programmed to check

data integrity in various modes. The USC also has

facilities for modem controls in both channels. In

applications where these controls are not needed, the

modem controls may be used for general-purpose I/

O. The same holds true for most of the other pins in

each channel.

Interrupts are supported with a daisy-chain hierarchy,

with the two channels having completely separate

interrupt structures.

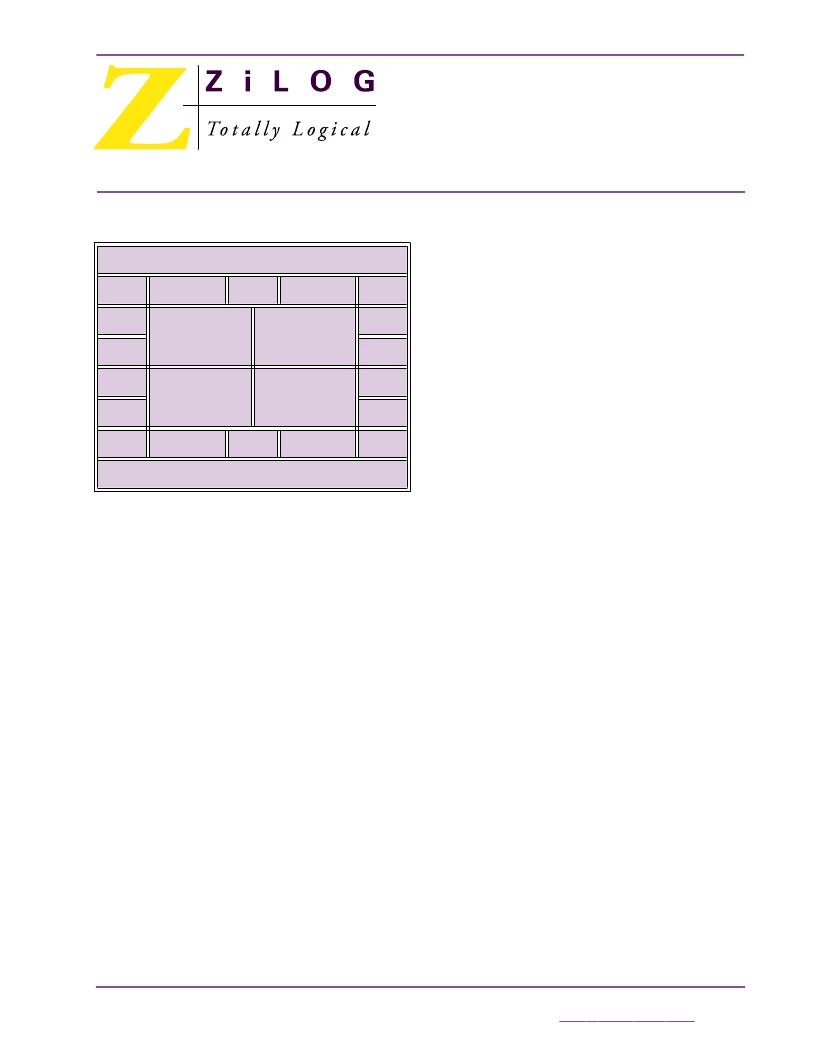

Modem/Control Logic

CTR

BRG

DPLL

BRG

CTR

CRC

Transmit

Logic

Receive

Logic

CRC

FIFO

FIFO

FIFO

Transmit

Logic

Receive

Logic

FIFO

CRC

CRC

CTR

BRG

DPLL

BRG

CTR

Modem/Control Logic

Z16C30

USC U

C

ONTROLLER

NIVERSAL

S

ERIAL

PB000300-SCC0399

相關PDF資料 |

PDF描述 |

|---|---|

| Z16C32 | Integrated Universal Serial Controller(數(shù)據(jù)通信用集成通用串行控制器) |

| Z16C35 | CMOS ISCC INTEGRATED SERIAL COMMUNICATIONS CONTROLLER |

| Z16C3510FEC | CMOS ISCC INTEGRATED SERIAL COMMUNICATIONS CONTROLLER |

| Z16C3510FED | CMOS ISCC INTEGRATED SERIAL COMMUNICATIONS CONTROLLER |

| Z16C3510FEE | CMOS ISCC INTEGRATED SERIAL COMMUNICATIONS CONTROLLER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| Z16C30_08 | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:CMOS USC Universal Serial Controller |

| Z16C3001ZCO | 功能描述:開發(fā)板和工具包 - 其他處理器 Z16C30 PC/AT Kit RoHS:否 制造商:Freescale Semiconductor 產品:Development Systems 工具用于評估:P3041 核心:e500mc 接口類型:I2C, SPI, USB 工作電源電壓: |

| Z16C3010AEC | 功能描述:輸入/輸出控制器接口集成電路 10MHz CMOS USC XTEMP RoHS:否 制造商:Silicon Labs 產品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| Z16C3010AEC00TR | 功能描述:IC Z16C30 MCU USC 100VQFP RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:USC® 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| Z16C3010AEG | 功能描述:輸入/輸出控制器接口集成電路 10MHz CMOS USC XTEMP RoHS:否 制造商:Silicon Labs 產品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。