- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376461 > XRT73LC03AIV (EXAR CORP) 3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT PDF資料下載

參數(shù)資料

| 型號(hào): | XRT73LC03AIV |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PQFP120 |

| 封裝: | 14 X 20 MM, LQFP-120 |

| 文件頁(yè)數(shù): | 41/61頁(yè) |

| 文件大?。?/td> | 720K |

| 代理商: | XRT73LC03AIV |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)當(dāng)前第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

XRT73LC03A

3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT

REV. 1.0.1

39

Decoder detects this particular pattern, then it substi-

tutes these bits with a “0000" pattern.

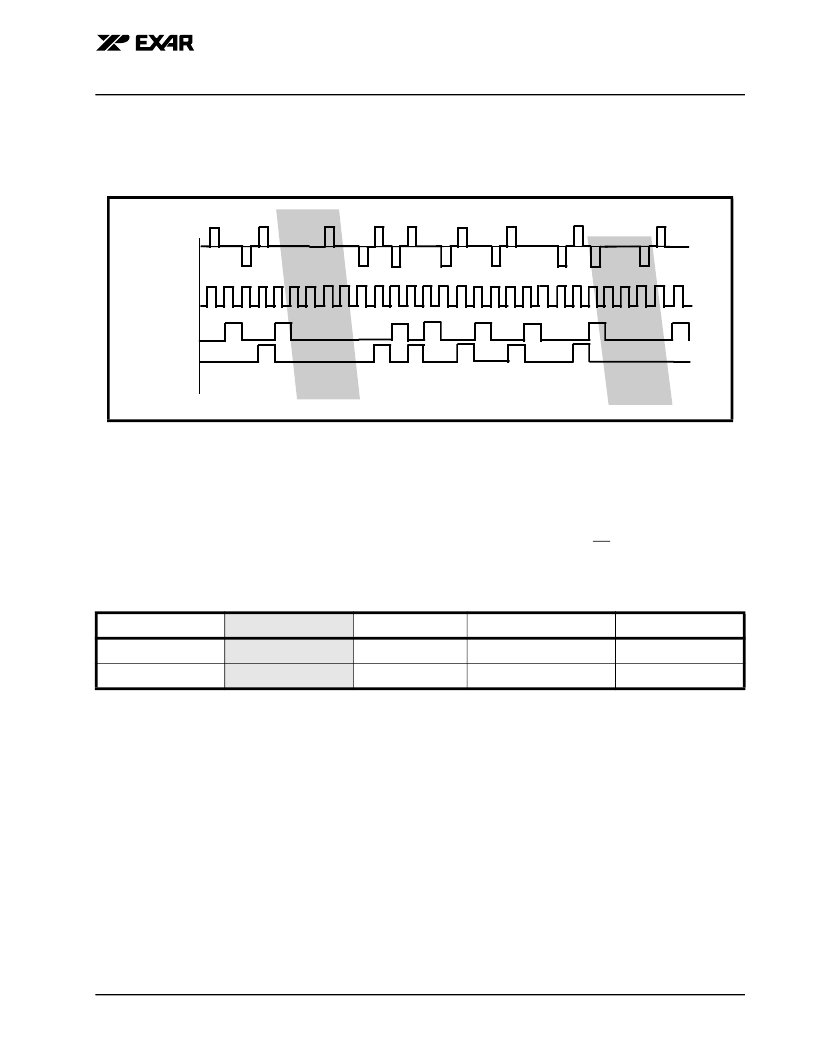

Figure 25 illustrates the HDB3 Decoder at work with

two separate Zero Suppression patterns, in the in-

coming Dual-Rail Data Stream.

N

OTE

:

If the HDB3 Decoder detects any bipolar violation

(e.g., "V") pulses that is not in accordance with the HDB3

Line Code format, or if the HDB3 Decoder detects a string

of 4 (or more) "0’s" in the incoming line signal, then the

HDB3 Decoder flags this event as a Line Code Violation by

pulsing the LCV output pin “High".

3.4.3

The XRT73LC03A can enable or disable the HDB3/

B3ZS Decoder blocks by either of the following

means.

a. Operating in the HOST Mode

Enable the HDB3/B3ZS Decoder block of Channel(n)

by writing a "0" into the

(SR/DR)_(n)

bit-field within

Command Register CR3-(n), as illustrated below.

Configuring the HDB3/B3ZS Decoder

b. Operating in the Hardware Mode

To globally enable all HDB3/B3ZS Decoder blocks in

the XRT73LC03A, pull the ENDECDIS input pin

“Low". To globally disable all HDB3/B3ZS Decoder

blocks in the XRT73LC03A and configure the

XRT73LC03A to transmit and receive in an AMI for-

mat, pull the ENDECDIS input pin "High".

3.5

LOS D

ECLARATION

/C

LEARANCE

Each channel of the XRT73LC03A contains circuitry

that monitors the following two parameters associat-

ed with the incoming line signals.

1.

The amplitude of the incoming line signal via the

RTIP and RRing inputs.

2.

The number of pulses detected in the incoming

line signal within a certain amount of time.

If a given channel of the XRT73LC03A determines

that the incoming line signal is missing due to either

insufficient amplitude or a lack of pulses in the incom-

ing line signal, it declares a Loss of Signal (LOS) con-

dition. The channel declares the LOS condition by

toggling its respective RLOS_(n) output pin “High”

and by setting its corresponding RLOS_(n) bit field in

Command Register 0 or Command Register 8 to "1".

Conversely, if the channel determines that the incom-

ing line signal has been restored (e.g., there is suffi-

cient amplitude and pulses in the incoming line sig-

nal), it clears the LOS condition by toggling its re-

spective RLOS_(n) output pin "Low" and setting its

corresponding RLOS_(n) bit-field to "0".

In general, the LOS Declaration/Clearance scheme

that is employed in the XRT73LC03A is based upon

F

IGURE

25. A

N

E

XAMPLE

OF

HDB3 D

ECODING

Data

0 1 0 1 1 0 0 0 0 0 1 1 1 1 0 1 1 0 1 1 0 0 1 1 0 0 0 0 1

0 0 0 V

Line Signal

B 0 0 V

RPOS

RNEG

RCLK

COMMAND REGISTER CR2-(n)

D4

D3

D2

D1

D0

Reserved

ENDECDIS_(n)

ALOSDIS_(n)

DLOSDIS_(n)

REQEN_(n)

X

0

X

X

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT73LC04A | 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73LC04AIV | 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73R06 | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73R06IB | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73R12 | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT73LC03AIVF | 制造商:Exar Corporation 功能描述:Line Interface Unit 51.84Mbps DS3/E3/STS-1 Serial 120-Pin LQFP |

| XRT73LC03AIV-F | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 3-Ch DS3, E3, STS-1 RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT73LC04A | 制造商:EXAR 制造商全稱:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73LC04A_08 | 制造商:EXAR 制造商全稱:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73LC04AES | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。