- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376461 > XRT7295AE_03 (Exar Corporation) E3 (34.368Mbps) Integrated line Receiver PDF資料下載

參數(shù)資料

| 型號: | XRT7295AE_03 |

| 廠商: | Exar Corporation |

| 英文描述: | E3 (34.368Mbps) Integrated line Receiver |

| 中文描述: | E3展(34.368Mbps)綜合線路接收器 |

| 文件頁數(shù): | 5/15頁 |

| 文件大小: | 861K |

| 代理商: | XRT7295AE_03 |

XRT7295AE

5

Rev. 2.0.0

SYSTEM DESCRIPTION

Receive Path Configurations

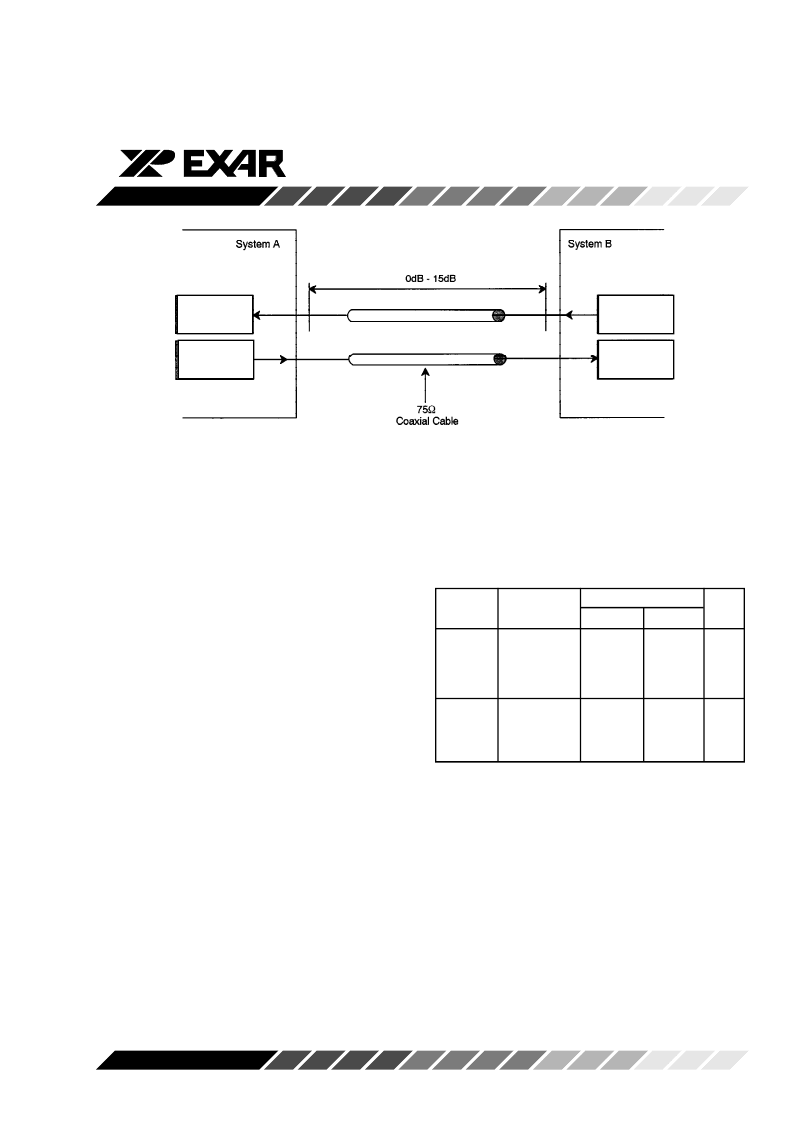

The diagram in Figure 2 shows a typical system

application for the XRT7295AE. In the receive signal

path (see Figure 1), the internal equalizer can be

included by setting REQB=0 or bypass by setting

REQB=1. The equalizer bypass option allows easy

interfacing of the XRT7295AE into systems already

containing the external equalizers. Figure 3 illustrates

the receive path option for two separate cases.

In case 1, the signal from the coaxial cable feeds

directly into the R

IN

input. In this mode, the user should

set REQB=0, engaging the equalizer in the data path

if the cable loss is greater than 6dB. If the cable loss

is less than 6dB, the equalizer is bypassed by setting

the REQB=1.

In case 2, an external line and equalizer network

precedes the XRT7295AE. In this mode, the signal at

R

IN

is already equalized, and the on-chip equalizer

should be bypassed by setting REQB1=1. In both

cases, the signal at R

IN

must meet the amplitude limits

described in Table 1.

The recommended receive termination is also shown in

Figure 3. The 75

resistor terminates the coaxial cable

with its characteristic impedance. In Figure 3 case 2,

if the fixed equalizer includes the line termination, the

75

resistor is not required. The signal is AC coupled

through the 0.01

μ

F capacitor to R

IN

. The DC bias at R

IN

is generated internally. The input capacitance at the

R

IN

pin is typically 2.8pF (SOJ package).

Pulse Mask at the 34.368 Mbps Interface

Table 2 shows the pulse specifications at the transmit-

ter output post and Figure 4 shows the pulse mask

requirement for E3 as recommended in G.703.

Minimum Signal

REQB

LOSTHR

SOJ2

DIP

Unit3

0

0

80

115

mV pk

V

DD

/2

60

85

mV pk

V

DD

40

60

mV pk

1

0

80

115

mV pk

V

DD

/2

80

115

mV pk

V

DD

80

115

mV pk

NOTES:

1

Maximum input amplitude under all conditions is 1.1

Vpk.

2

The SOJ package performance is enhanced by de-

creased package parasitics.

Although system designers typically use power in dBm

to describe input levels, the XRT7295AE responds to

peak input signal amplitude. Therefore, the

XRT7295AE input signal limits are given in mV pk.

3

Table 1. Receive Input Signal Amplitude

Requirements

Figure 2. Application Diagram

XRT7295AE

XRT7296

Transmitter

XRT7295AE

XRT7296

Transmitter

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT7295AEIW | E3 (34.368Mbps) Integrated line Receiver |

| XRT7295AT | DS3/Sonet STS-1 Integrated Line Receiver |

| XRT7295ATIW | DS3/Sonet STS-1 Integrated Line Receiver |

| XRT7295 | () |

| XRT7296 | INTEGRATED LINE TRANSMITTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT7295AEIW | 功能描述:外圍驅(qū)動器與原件 - PCI E3 Line Receiver RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT7295AEIW-F | 功能描述:外圍驅(qū)動器與原件 - PCI E3 Line Receiver RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT7295AEIWTR | 功能描述:外圍驅(qū)動器與原件 - PCI E3 Line Receiver RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT7295AEIWTR-F | 功能描述:外圍驅(qū)動器與原件 - PCI E3 Line Receiver RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT7295AT | 制造商:EXAR 制造商全稱:EXAR 功能描述:DS3/Sonet STS-1 Integrated Line Receiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。