- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16499 > XR16M654IV80-0A-EB (Exar Corporation)EVAL BOARD FOR XR16M654-A 80LQFP PDF資料下載

參數(shù)資料

| 型號: | XR16M654IV80-0A-EB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 21/58頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16M654-A 80LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

XR16M654/654D

28

1.62V TO 3.63V QUAD UART WITH 64-BYTE FIFO

REV. 1.0.0

4.0

INTERNAL REGISTER DESCRIPTIONS

4.1

Receive Holding Register (RHR) - Read- Only

4.2

Transmit Holding Register (THR) - Write-Only

4.3

Interrupt Enable Register (IER) - Read/Write

The Interrupt Enable Register (IER) masks the interrupts from receive data ready, transmit empty, line status

and modem status registers. These interrupts are reported in the Interrupt Status Register (ISR).

4.3.1

IER versus Receive FIFO Interrupt Mode Operation

When the receive FIFO (FCR BIT-0 = 1) and receive interrupts (IER BIT-0 = 1) are enabled, the RHR interrupts

(see ISR bits 2 and 3) status will reflect the following:

A. The receive data available interrupts are issued to the host when the FIFO has reached the programmed

trigger level. It will be cleared when the FIFO drops below the programmed trigger level.

B. FIFO level will be reflected in the ISR register when the FIFO trigger level is reached. Both the ISR register

status bit and the interrupt will be cleared when the FIFO drops below the trigger level.

C. The receive data ready bit (LSR BIT-0) is set as soon as a character is transferred from the shift register to

the receive FIFO. It is reset when the FIFO is empty.

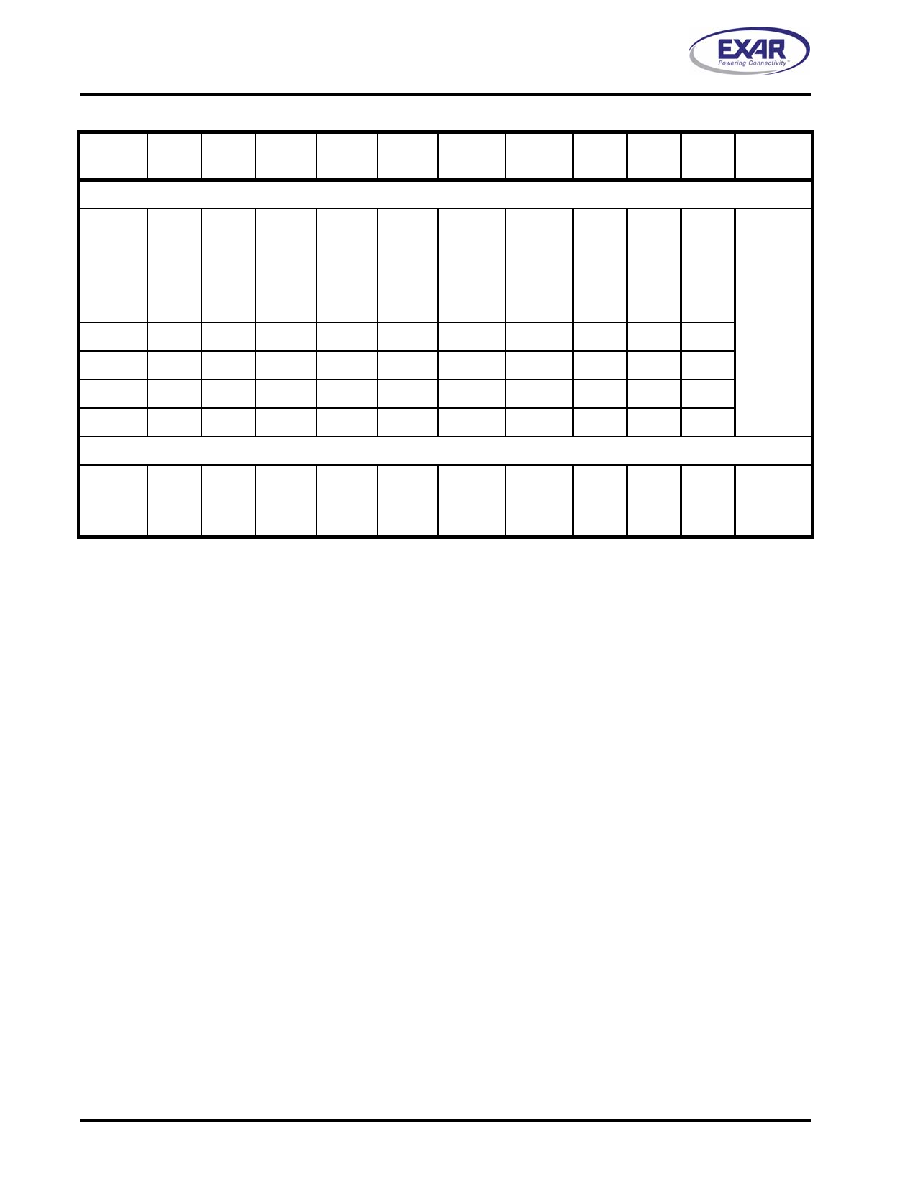

Enhanced Registers

0 1 0

EFR

RD/WR

Auto

CTS#

Enable

Auto

RTS#

Enable

Special

Char

Select

Enable

IER [7:4],

ISR [5:4],

FCR[5:4],

MCR[7:5],

DLD

Soft-

ware

Flow

Cntl

Bit-3

Soft-

ware

Flow

Cntl

Bit-2

Soft-

ware

Flow

Cntl

Bit-1

Soft-

ware

Flow

Cntl

Bit-0

LCR=0XBF

1 0 0

XON1

RD/WR

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 0 1

XON2

RD/WR

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 1 0

XOFF1 RD/WR

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 1 1

XOFF2 RD/WR

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

X X X

FSTAT

RD

RX-

RDYD#

RX-

RDYC#

RX-

RDYB#

RX-

RDYA#

TX-

RDYD#

TX-

RDYC#

TX-

RDYB#

TX-

RDYA#

FSRS# pin is

a logic 0. No

address lines

required.

TABLE 10: INTERNAL REGISTERS DESCRIPTION. SHADED BITS ARE ENABLED WHEN EFR BIT-4=1

ADDRESS

A2-A0

REG

NAME

READ/

WRITE

BIT-7

BIT-6

BIT-5

BIT-4

BIT-3

BIT-2

BIT-1

BIT-0

COMMENT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-24N-EX | CONVERTER MOD DC/DC 18.5V 75W |

| EMC06DRYH-S93 | CONN EDGECARD 12POS DIP .100 SLD |

| LK1608R56M-T | INDUCTOR MULTILAYER .56UH 0603 |

| 5349565-1 | FOMM50 LEAD 2.5 TZ SC/PC-SC/PC |

| VI-J6V-EZ-S | CONVERTER MOD DC/DC 5.8V 25W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16M654IV80-0B-EB | 功能描述:界面開發(fā)工具 Eval Board for XR16M654IV80-0B RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR16M654IV80-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16M654IV80TR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 1.8V/2.5V/3.3V 80-Pin LQFP T/R |

| XR16M670 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE UART WITH 32-BYTE FIFO |

| XR16M670IB25 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE UART WITH 32-BYTE FIFO |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。