- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16499 > XR16M654IL-0B-EVB (Exar Corporation)EVAL BOARD FOR XR16M654-B 48QFN PDF資料下載

參數(shù)資料

| 型號: | XR16M654IL-0B-EVB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 56/58頁 |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR16M654-B 48QFN |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當前第56頁第57頁第58頁

XR16M654/654D

7

REV. 1.0.0

1.62V TO 3.63V QUAD UART WITH 64-BYTE FIFO

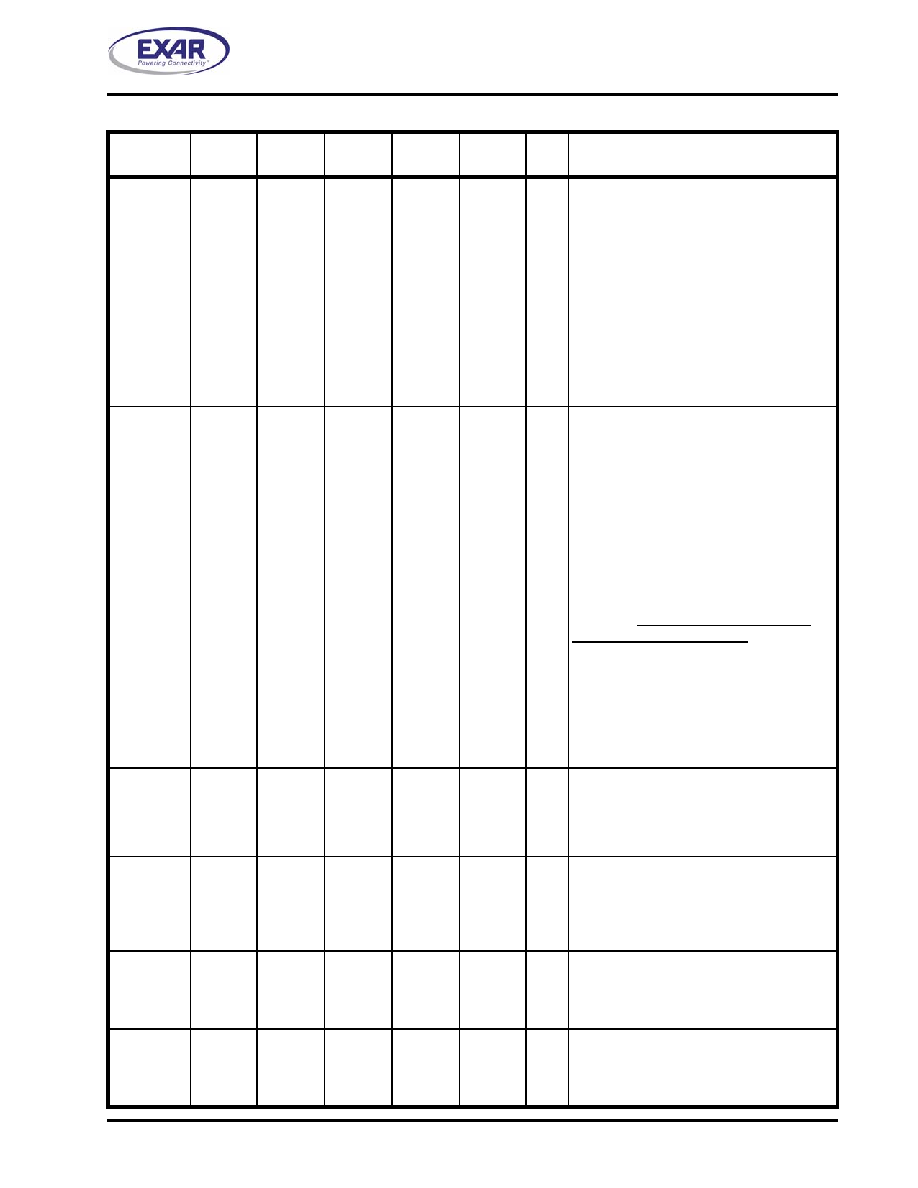

INTB

INTC

INTD

(N.C.)

10

26

32

12

37

43

21

49

55

14

48

54

18

63

69

O

When 16/68# pin is HIGH for Intel bus inter-

face, these ouputs become the interrupt

outputs for channels B, C, and D. The out-

put state is defined by the user through the

software setting of MCR[3]. The interrupt

outputs are set to the active mode when

MCR[3] is set to a logic 1 and are set to the

three state mode when MCR[3] is set to a

logic 0 (default). See MCR[3].

When 16/68# pin is LOW for Motorola bus

interface, these outputs are unused and will

stay at logic zero level. Leave these out-

puts unconnected.

INTSEL

38

-

65

67

87

I

Interrupt Select (active high, input with

internal pull-down).

When 16/68# pin is HIGH for Intel bus inter-

face, this pin can be used in conjunction

with MCR bit-3 to enable or disable the INT

A-D pins or override MCR bit-3 and enable

the interrupt outputs. Interrupt outputs are

enabled continuously when this pin is

HIGH. MCR bit-3 enables and disables the

interrupt output pins. In this mode, MCR

bit-3 is set to a logic 1 to enable the continu-

ous output. See MCR bit-3 description for

full detail. This pin must be LOW in the

Motorola bus interface mode. For the 64

pin packages, this pin is bonded to VCC

internally in the XR16M654D so the INT

outputs operate in the continuous interrupt

mode. This pin is bonded to GND internally

in the XR16M654 and therefore requires

setting MCR bit-3 for enabling the interrupt

output pins.

TXRDYA#

TXRDYB#

TXRDYC#

TXRDYD#

-

5

25

56

81

O

UART channels A-D Transmitter Ready

(active low). The outputs provide the TX

FIFO/THR status for transmit channels A-D.

See Table 5. If these outputs are unused,

leave them unconnected.

RXRDYA#

RXRDYB#

RXRDYC#

RXRDYD#

-

100

31

50

82

O

UART channels A-D Receiver Ready

(active low). This output provides the RX

FIFO/RHR status for receive channels A-D.

See Table 5. If these outputs are unused,

leave them unconnected.

TXRDY#

-

39

35

45

O

Transmitter Ready (active low). This output

is a logically ANDed status of TXRDY# A-

D. See Table 5. If this output is unused,

leave it unconnected.

RXRDY#

-

38

34

44

O

Receiver Ready (active low). This output is

a logically ANDed status of RXRDY# A-D.

See Table 5. If this output is unused, leave

it unconnected.

Pin Description

NAME

48-QFN

PIN #

64-LQFP

PIN #

68-PLCC

PIN#

80-LQFP

PIN #

100-QFP

PIN #

TYPE

DESCRIPTION

相關PDF資料 |

PDF描述 |

|---|---|

| RMC13DREI | CONN EDGECARD 26POS .100 EYELET |

| 5504971-7 | CA 62.5/125 LDDZP SCDUP SCDUP |

| RBC12DCAH-S189 | CONN EDGECARD 24POS R/A .100 SLD |

| RCB22DHRN | CONN CARD EXTEND 44POS .050" |

| LK1608R15M-T | INDUCTOR MULTILAYER .15UH 0603 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XR16M654IL48 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V QUAD UART WITH 64-BYTE FIFO |

| XR16M654IL48-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16M654IL48TR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 1.8V/2.5V/3.3V 48-Pin QFN EP T/R |

| XR16M654IQ100 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V QUAD UART WITH 64-BYTE FIFO |

| XR16M654IQ100-0A-EB | 功能描述:界面開發(fā)工具 Eval Board for XR16M654IQ100-0A RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復。