- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄16502 > XR16M554DIV-0B-EVB (Exar Corporation)EVAL BOARD FOR XR16M554DB 64LQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XR16M554DIV-0B-EVB |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 9/46頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR16M554DB 64LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

XR16M554/554D

17

REV. 1.0.0

1.62V TO 3.63V QUAD UART WITH 16-BYTE FIFO

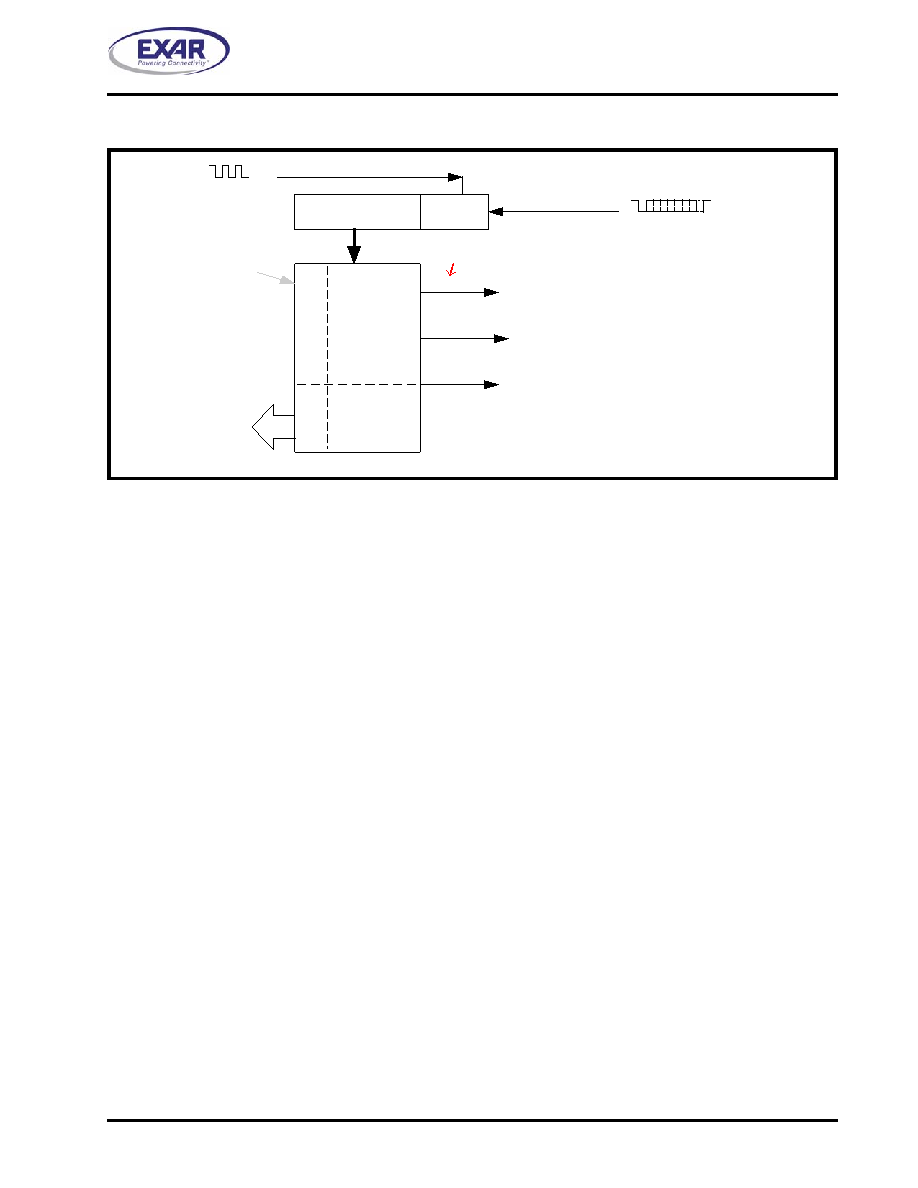

FIGURE 10. RECEIVER OPERATION IN FIFO

Rece ive Da ta S hift

R egister (R S R )

R X FIFO 1

16X C lock

E

rro

rTags

(1

6

-s

e

ts

)

Er

ro

rT

a

g

s

in

LS

R

bit

s

4:

2

R ece ive D ata C haracte rs

D a ta B it

V alidation

Receive

D ata FIF O

Receive

Data

Rece ive Da ta

B yte and E rrors

R H R Interrupt (IS R bit-2 ) prog ram m ed for

de sired FIFO trigger level.

FIFO is E nab led by F C R b it-0=1

A sking fo r stop ping d ata w h en da ta fills ab ove th e flow

con trol trig ger le vel to su spend rem o te tran sm itter.

A sking for sendin g data w hen data falls below the flow

con trol trig ger le vel to restart rem ote transm itter.

16 bytes by 11-bit w ide

FIFO

T rigger=8

D ata falls to

4

D ata fills to

14

E xam ple

: - R X F IF O trigger level selected at 8 bytes

(See N ote Below )

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RCC10DRYI-S734 | CONN EDGECARD 20POS DIP .100 SLD |

| VE-J6M-EZ-S | CONVERTER MOD DC/DC 10V 25W |

| H3DKH-3036G | IDC CABLE - HKR30H/AE30G/HPK30H |

| NS10145T221MNA | INDUCTOR POWER 220UH 20% SMD |

| RBC05DRAI-S734 | CONN EDGECARD 10POS .100 R/A PCB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16M554DIV64 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V QUAD UART WITH 16-BYTE FIFO |

| XR16M554DIV64-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16M554IJ-0A-EVB | 功能描述:界面開(kāi)發(fā)工具 Eval Board for XR16M554IJ-0A RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類(lèi)型:RS-485 工具用于評(píng)估:ADM3485E 接口類(lèi)型:RS-485 工作電源電壓:3.3 V |

| XR16M554IJ-0B-EVB | 功能描述:界面開(kāi)發(fā)工具 Eval Board for XR16M554IJ-0B RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類(lèi)型:RS-485 工具用于評(píng)估:ADM3485E 接口類(lèi)型:RS-485 工作電源電壓:3.3 V |

| XR16M554IJ68 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V QUAD UART WITH 16-BYTE FIFO |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。