- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4204 > XCV812E-7FG900C (Xilinx Inc)IC FPGA 1.8V C-TEMP 900-FBGA PDF資料下載

參數(shù)資料

| 型號: | XCV812E-7FG900C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 65/118頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V C-TEMP 900-FBGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標準包裝: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB數(shù): | 4704 |

| 邏輯元件/單元數(shù): | 21168 |

| RAM 位總計: | 1146880 |

| 輸入/輸出數(shù): | 556 |

| 門數(shù): | 254016 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 900-BBGA |

| 供應商設備封裝: | 900-FBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

Module 2 of 4

DS025-2 (v3.0) March 21, 2014

46

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Termination Resistor Packs

Resistor packs are available with the values and the config-

uration required for LVDS and LVPECL termination from

Bourns, Inc., as listed in Table. For pricing and availability,

please contact Bourns directly at www.bourns.com.

LVDS Design Guide

The SelectI/O library elements have been expanded for Vir-

tex-E devices to include new LVDS variants. At this time all

of the cells might not be included in the Synthesis libraries.

The 2.1i-Service Pack 2 update for Alliance and Foundation

software includes these cells in the VHDL and Verilog librar-

ies. It is necessary to combine these cells to create the

P-side (positive) and N-side (negative) as described in the

input, output, 3-state and bidirectional sections.

Creating LVDS Global Clock Input Buffers

The global clock input buffer can be combined with the adja-

cent IOB to form an LVDS clock input buffer. The P-side

resides in the GCLKPAD location and the N-side resides in

the adjacent IO_LVDS_DLL site.

HDL Instantiation

Only one global clock input buffer is required to be instanti-

ated in the design and placed on the correct GCLKPAD

location. The N-side of the buffer is reserved and no other

IOB is allowed to be placed on this location.

In the physical device, a configuration option is enabled that

routes the pad wire to the differential input buffer located in

the GCLKIOB. The output of this buffer then drives the out-

put of the GCLKIOB cell. In EPIC it appears that the second

buffer is unused. Any attempt to use this location for another

purpose leads to a DRC error in the software.

VHDL Instantiation

gclk0_p : IBUFG_LVDS port map

(I=>clk_external, O=>clk_internal);

Verilog Instantiation

IBUFG_LVDS gclk0_p (.I(clk_external),

.O(clk_internal));

Location Constraints

All LVDS buffers must be explicitly placed on a device. For

the global clock input buffers this can be done with the fol-

lowing constraint in the UCF or NCF file.

NET clk_external LOC = GCLKPAD3;

GCLKPAD3 can also be replaced with the package pin

name, such as D17 for the BG432 package.

Optional N-Side

Some designers might prefer to also instantiate the N-side

buffer for the global clock buffer. This allows the top-level net

list to include net connections for both PCB layout and sys-

tem-level integration. In this case, only the output P-side

IBUFG connection has a net connected to it. Since the

N-side IBUFG does not have a connection in the EDIF net

list, it is trimmed from the design in MAP.

VHDL Instantiation

gclk0_p : IBUFG_LVDS port map

(I=>clk_p_external, O=>clk_internal);

gclk0_n : IBUFG_LVDS port map

(I=>clk_n_external, O=>clk_internal);

Verilog Instantiation

IBUFG_LVDS gclk0_p (.I(clk_p_external),

.O(clk_internal));

IBUFG_LVDS gclk0_n (.I(clk_n_external),

.O(clk_internal));

Location Constraints

All LVDS buffers must be explicitly placed on a device. For

the global clock input buffers this can be done with the fol-

lowing constraint in the UCF or NCF file.

NET clk_p_external LOC = GCLKPAD3;

NET clk_n_external LOC = C17;

Table 40:

Bourns LVDS/LVPECL Resistor Packs

Part Number

I/O Standard

Term.

for:

Pairs/

Pack

Pins

CAT16

LV2F6

LVDS

Driver

2

8

CAT16

LV4F12

LVDS

Driver

4

16

CAT16

PC2F6

LVPECL

Driver

2

8

CAT16

PC4F12

LVPECL

Driver

4

16

CAT16

PT2F2

LVDS/LVPECL

Receiver

2

8

CAT16

PT4F4

LVDS/LVPECL

Receiver

4

16

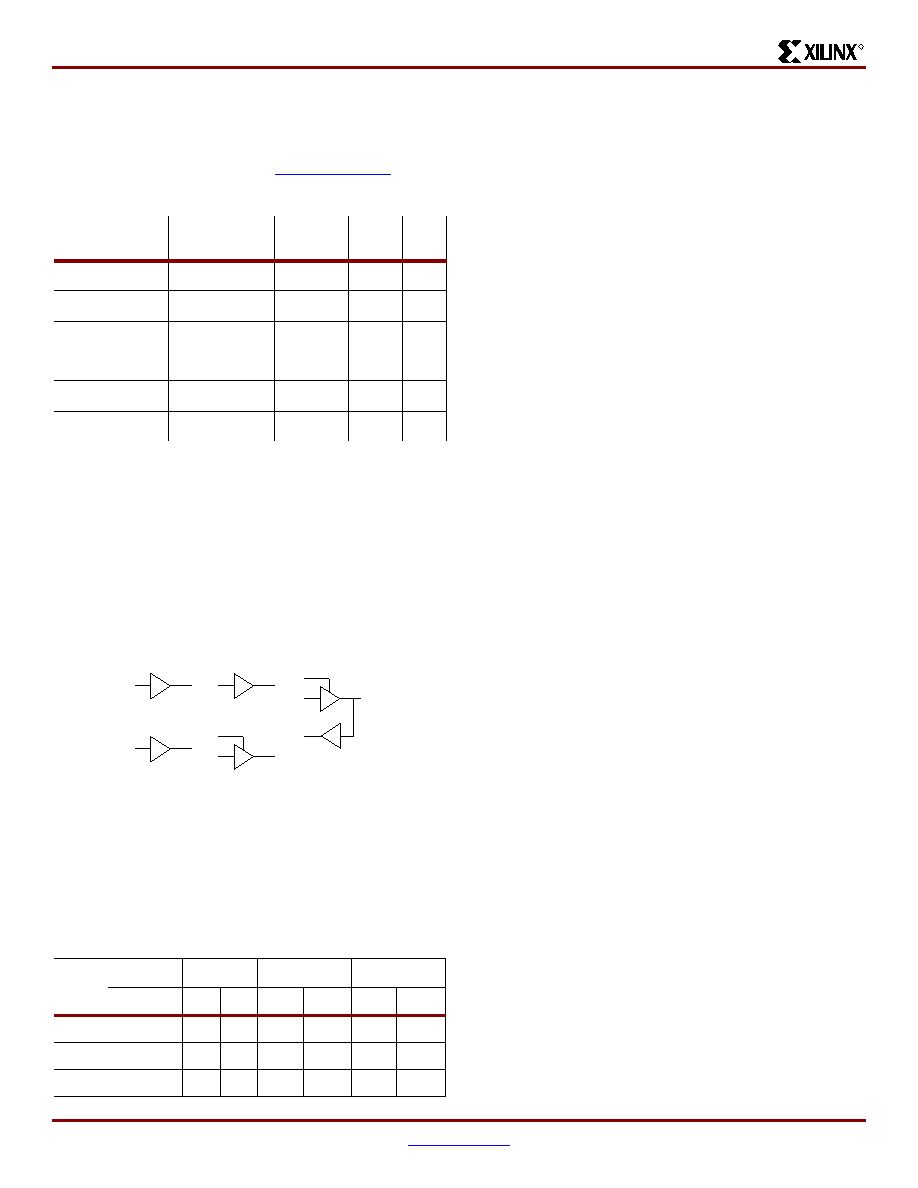

Figure 58: LVDS Elements

Table 41:

Global Clock Input Buffer Pair Locations

Pkg

Pair 3

Pair 2

Pair 0

PN

P

N

P

N

P

N

BG560

A17

C18

D17

E17

AJ17

AM18

AL17

AM17

FG676

E13

B13

C13

F14

AB13

AF13

AA14

AC14

FG900

C15

A15

E15

E16

AK16

AH16

AJ16

AF16

O

I

IBUF_LVDS

O

I

OBUF_LVDS

IOBUF_LVDS

O

T

I

OBUFT_LVDS

O

I

IBUFG_LVDS

IO

T

I

x133_22_122299

相關PDF資料 |

PDF描述 |

|---|---|

| XC6VLX240T-1FFG1759I | IC FPGA VIRTEX 6 241K 1759FFGBGA |

| XC6VLX240T-1FF1759I | IC FPGA VIRTEX 6 241K 1759FFBGA |

| XC5VLX110T-1FFG1136I | IC FPGA VIRTEX-5 110K 1136FBGA |

| XC5VLX110T-1FF1136I | IC FPGA VIRTEX-5 110K 1136FBGA |

| XC6VHX255T-1FFG1155C | IC FPGA VIRTEX 1156FCBGA |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV812E-7FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-8BG404C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-8BG404I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-8BG556C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-8BG556I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復。